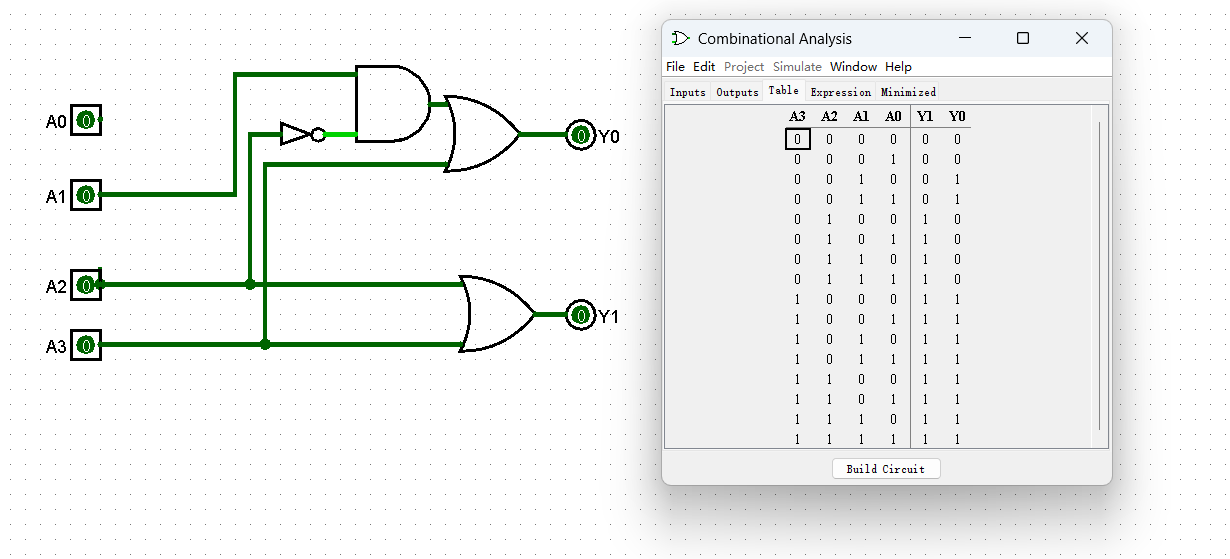

分析门电路

尝试分析一下门电路的行为和功能.

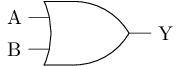

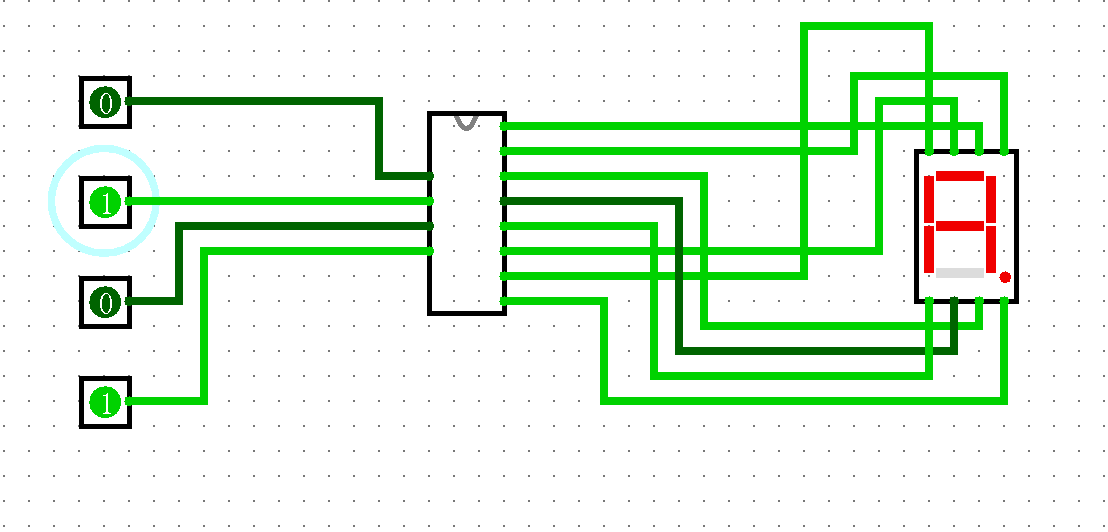

![[分析门电路.png]](/images/%E4%B8%80%E7%94%9F%E4%B8%80%E8%8A%AFF3/%E5%88%86%E6%9E%90%E9%97%A8%E7%94%B5%E8%B7%AF.png)

| A | B | P1 | P2 | N1 | N2 | Y |

|---|---|---|---|---|---|---|

| 0 | 0 | 导通 | 导通 | 截止 | 截止 | 1 |

| 0 | 1 | 导通 | 截止 | 截止 | 导通 | 0 |

| 1 | 0 | 截止 | 导通 | 导通 | 截止 | 0 |

| 1 | 1 | 截止 | 截止 | 导通 | 导通 | 0 |

根据上表分析,该电路实现了一个2输入或非门.

或门的晶体管结构

以下是或门的逻辑符号, 尝试画出或门的晶体管结构.

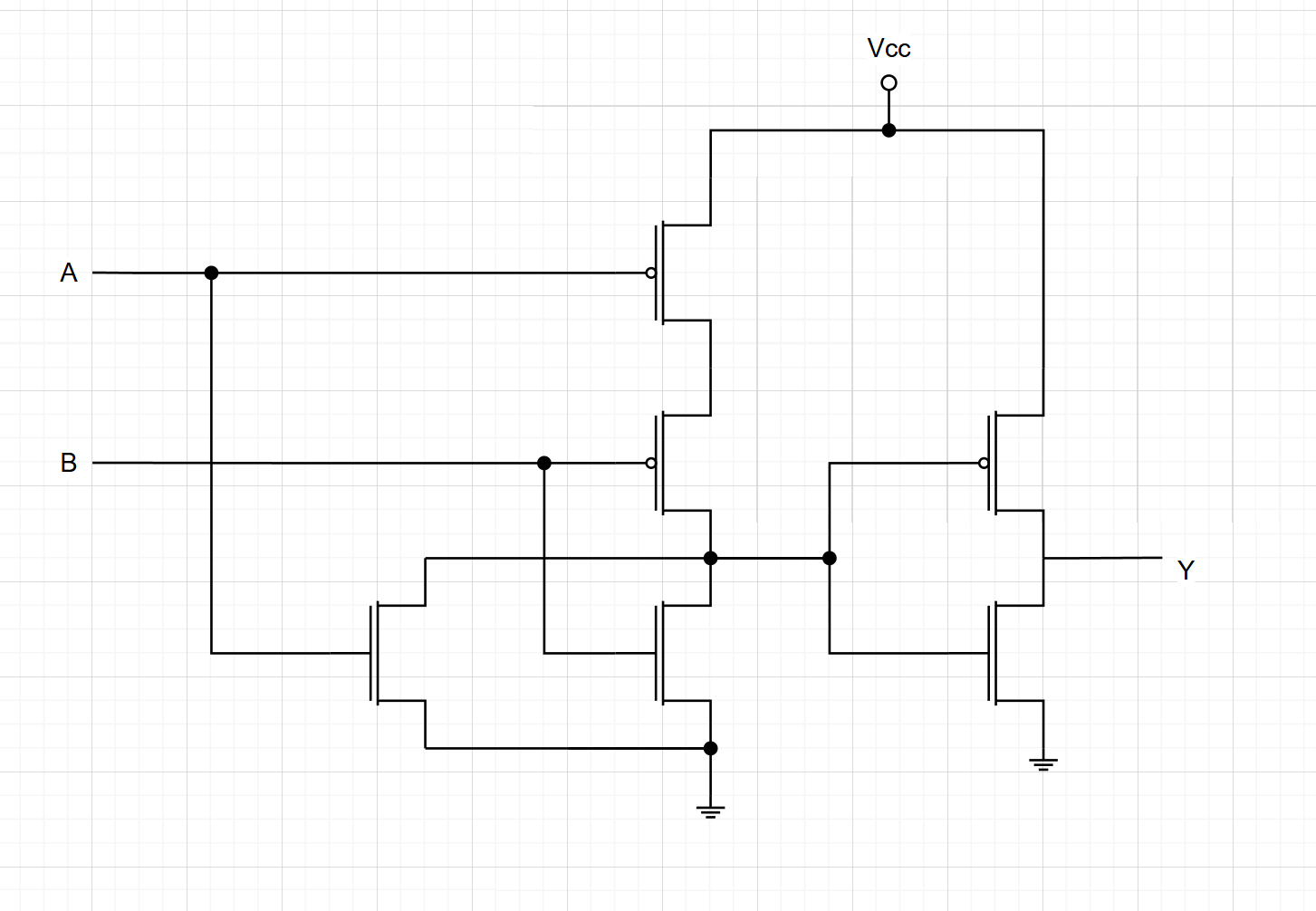

或门可以在上题或非门后串联一个非门电路构成,如下图所示:

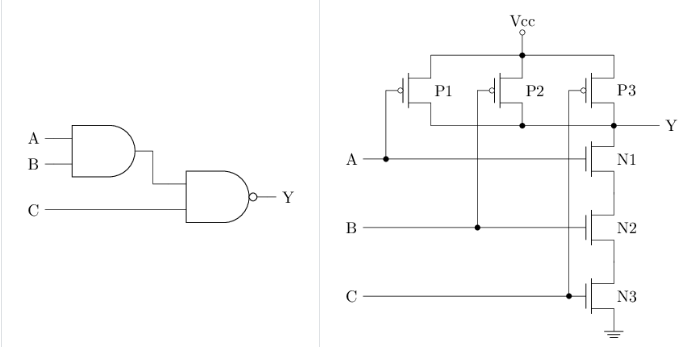

对比两种实现的晶体管所需要的数量

左图的使用一个与门和一个与非门实现,与门需要6个晶体管,与非门则需要4个晶体管,故共需要10个晶体管.

右图则仅需6个晶体管.

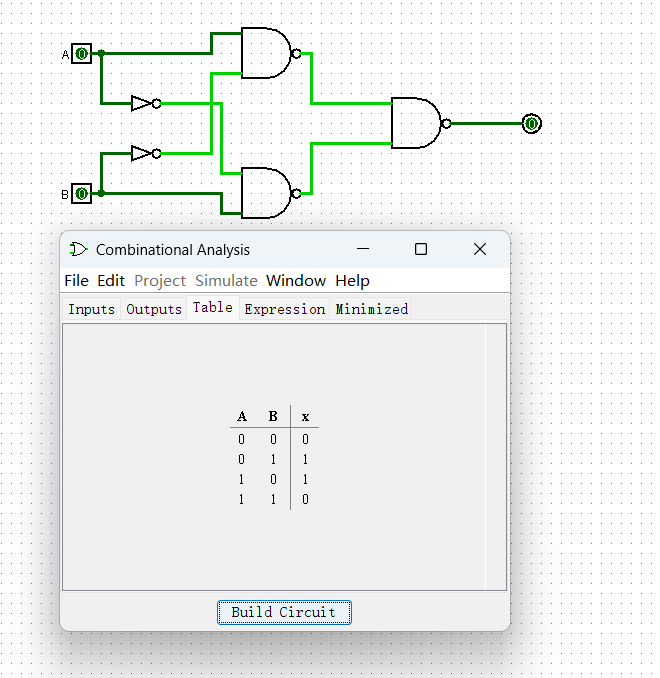

用其他门电路搭建异或门

尝试在 Logisim 中用上文提到的门电路搭建一个异或门. 搭建后, 通过仿真检查你的方案是否正确.

实现正确后, 计算你的方案使用了多少个晶体管.

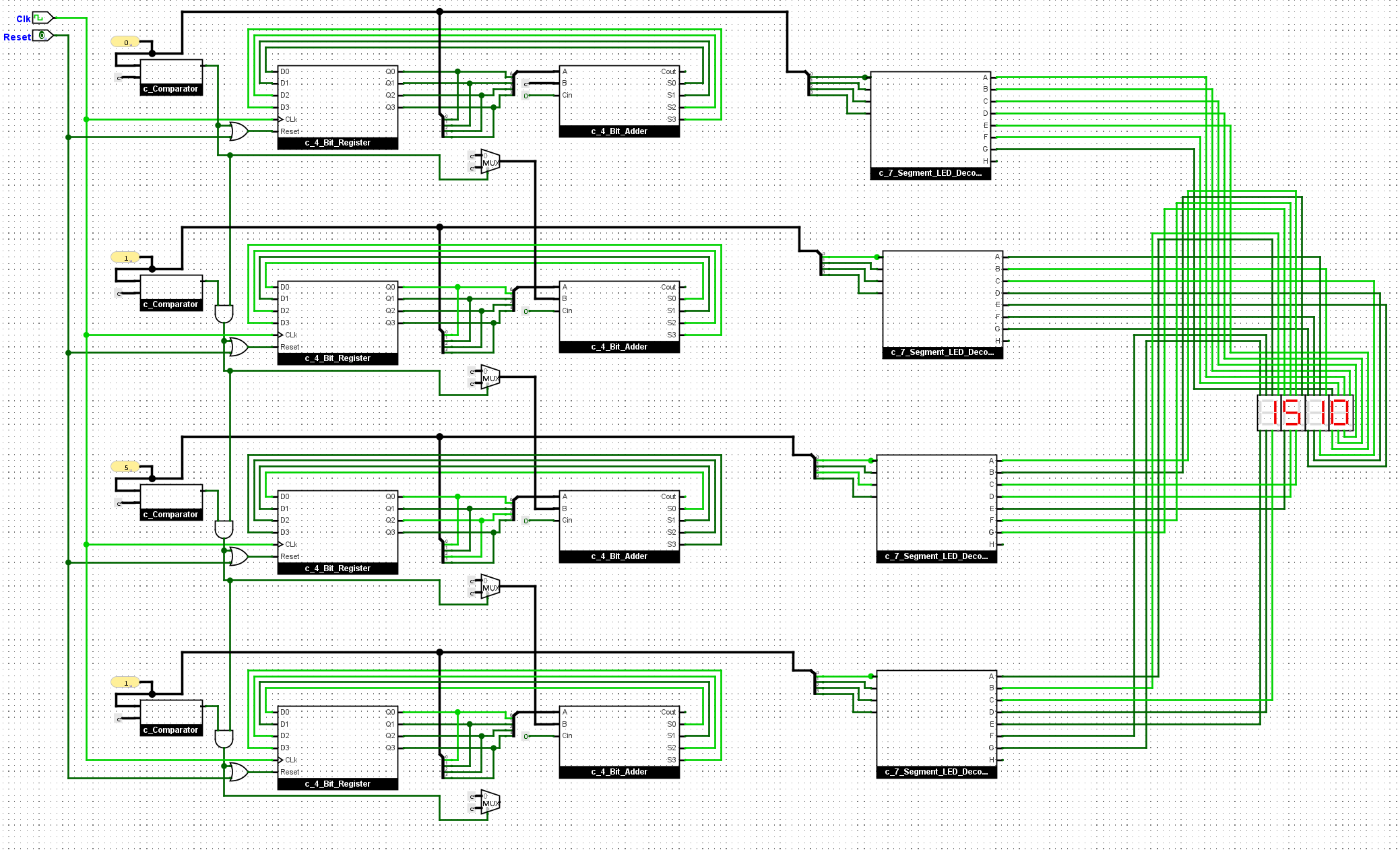

如图所示,使用了两个非门,三个与非门,共需16个晶体管

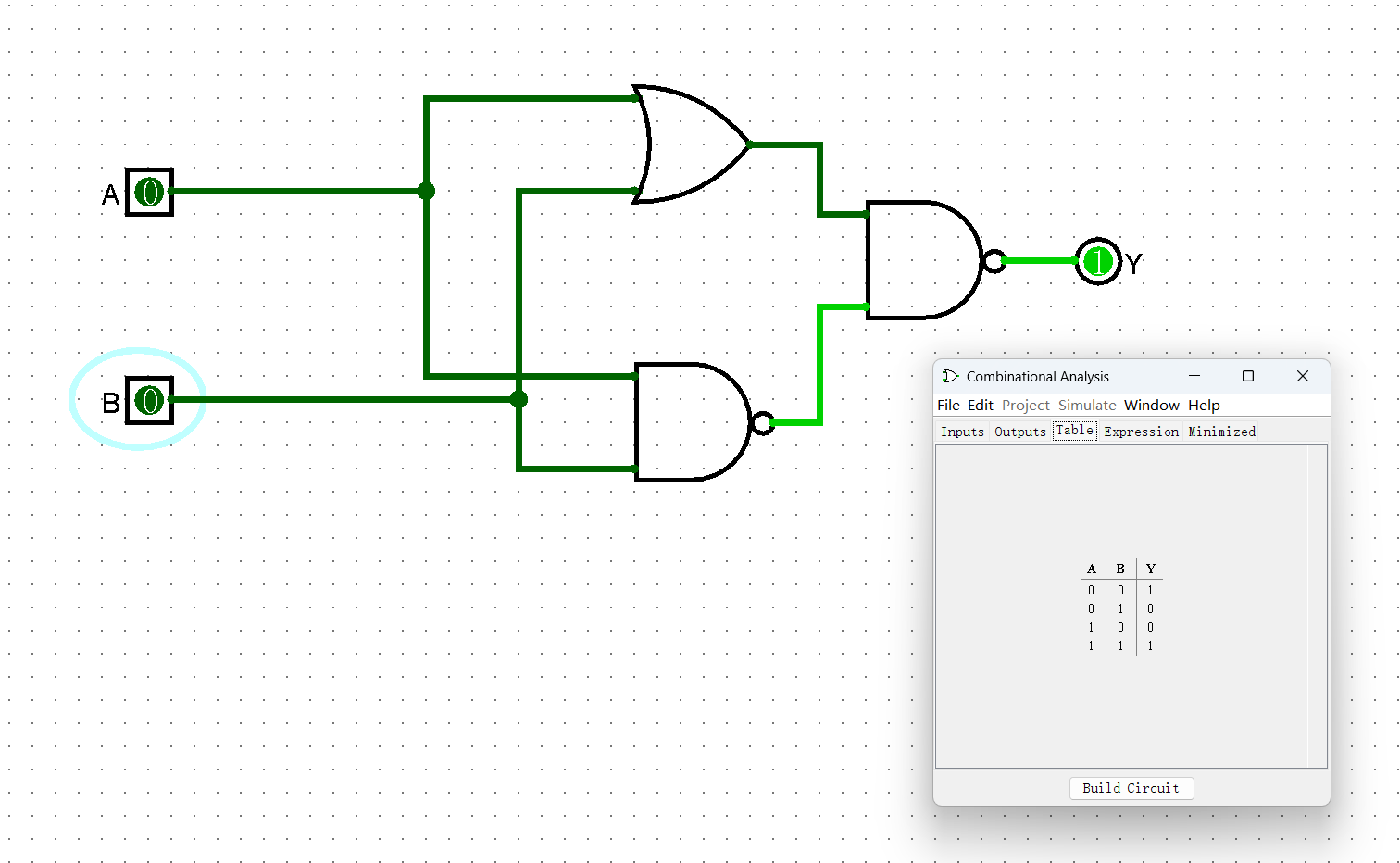

设计同或门

还有另一种操作是"同或"操作, 当输入A和B相同时, 结果为1, 否则为0. 同或操作可以认为是异或操作结果的取反.

尝试在Logisim中用上文提到的门电路搭建一个同或门. 搭建后, 通过仿真检查你的方案是否正确.

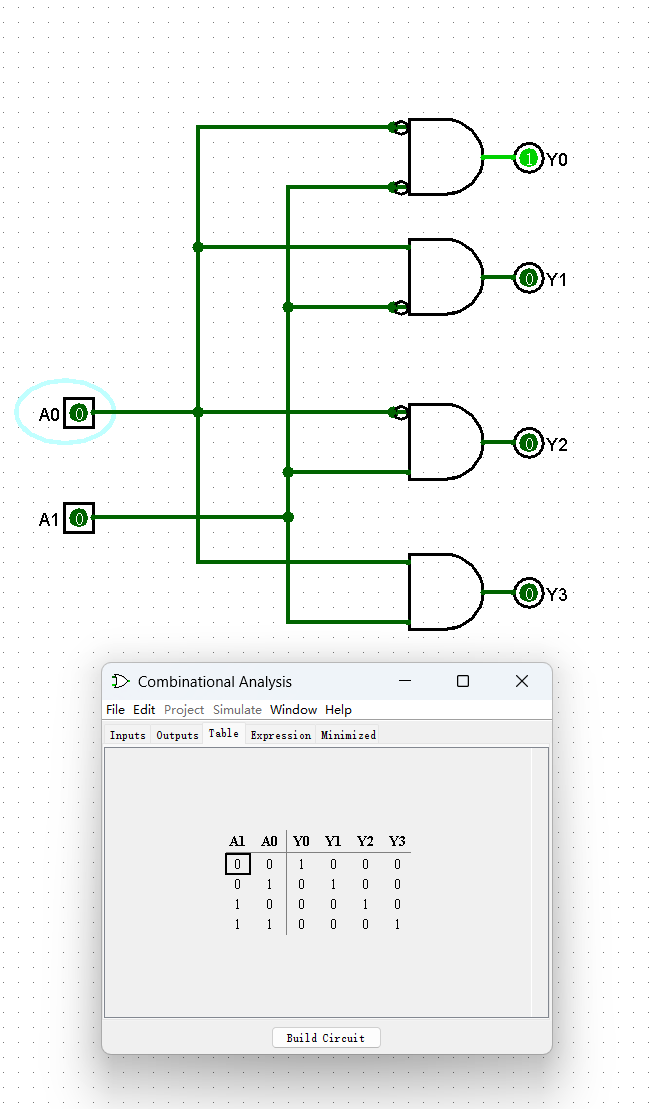

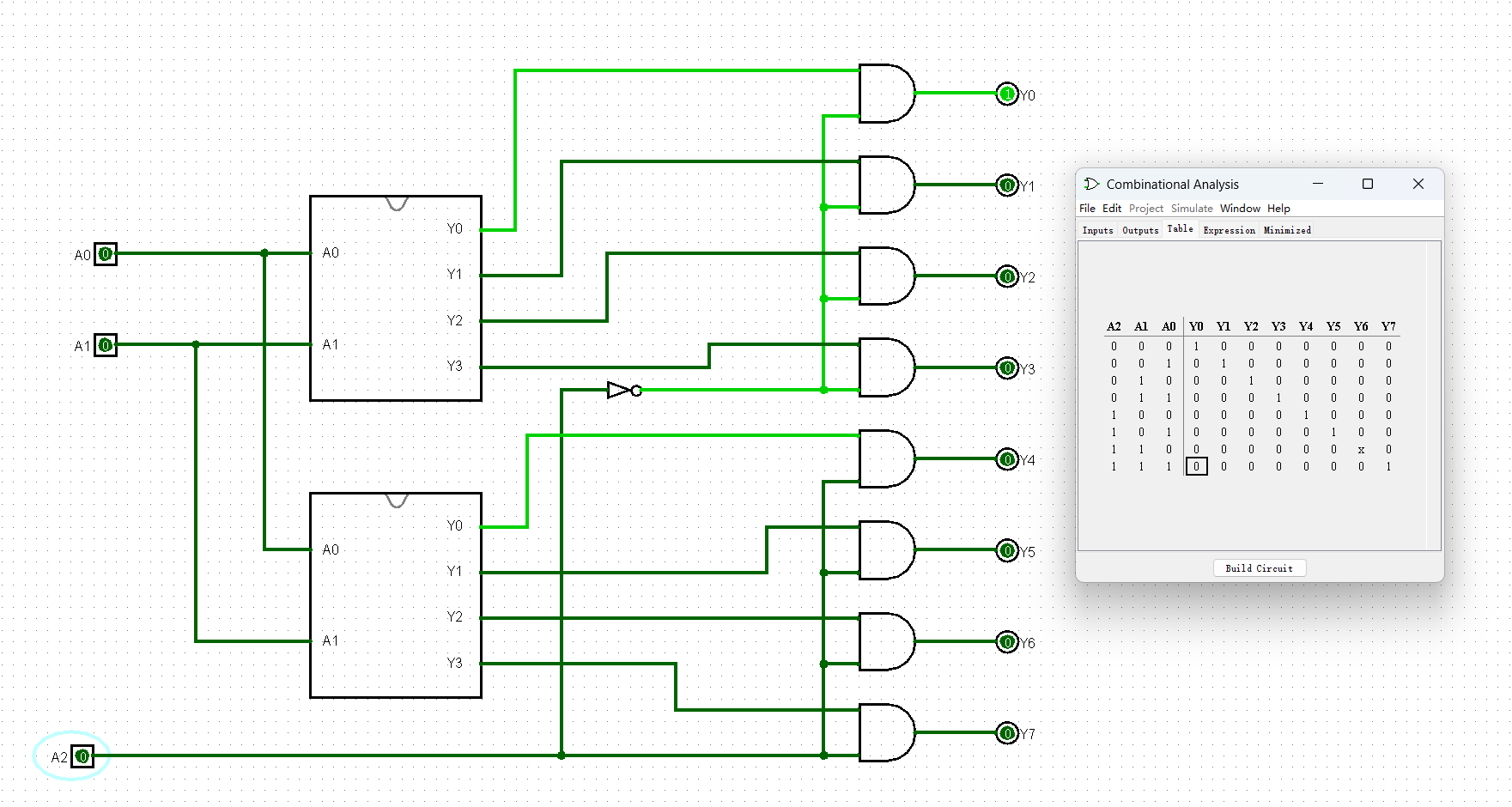

搭建2-4译码器

尝试在 Logisim 中用门电路搭建一个2-4译码器, 它有2位输入, 4位输出. 搭建后, 通过仿真检查你的方案是否正确.

如下图所示:

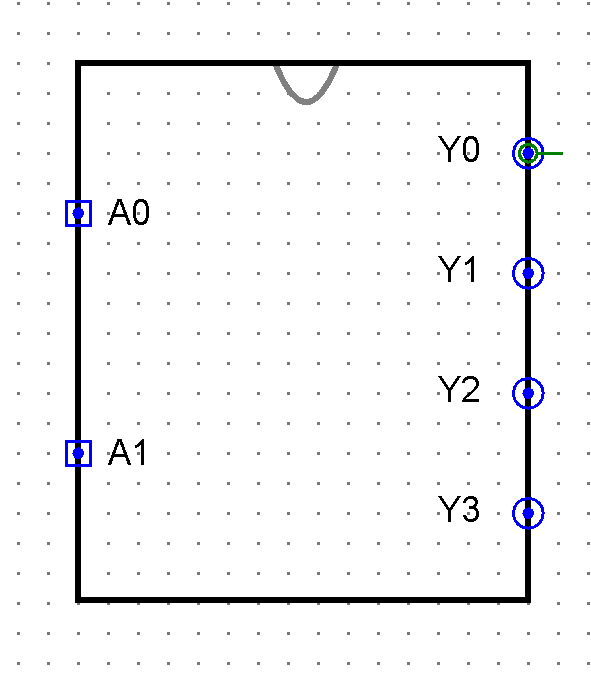

Logisim中的子电路功能

译码器在后续的数字电路设计中会经常用到, 为了避免用户重复设计相同的电路, Logisim 提供了子电路功能, 相应电路只需要设计一次, 后续即可反复实例化. 具体操作方式请阅读官方手册中的Subcircuits(子电路)部分.

子电路如图所示:

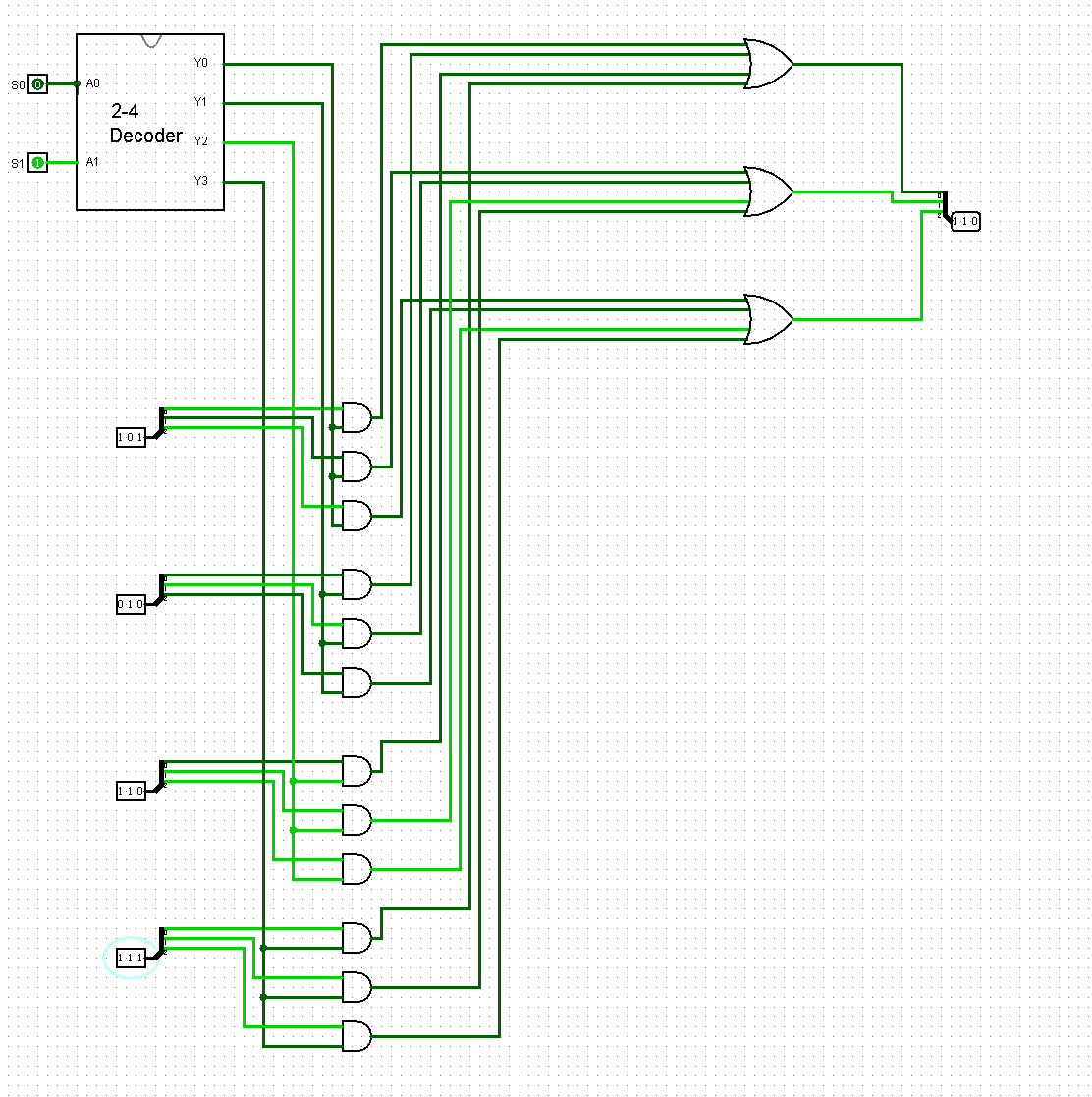

译码器的拓展

3-8译码器有3位输入, 8位输出. 尝试实例化若干个2-4译码器(具体数量交给你的思考), 并添加少量门电路, 从而实现3-8译码器的功能. 搭建后, 通过仿真检查你的方案是否正确.

使用2个2-4译码器组成3-8译码器,如图所示:

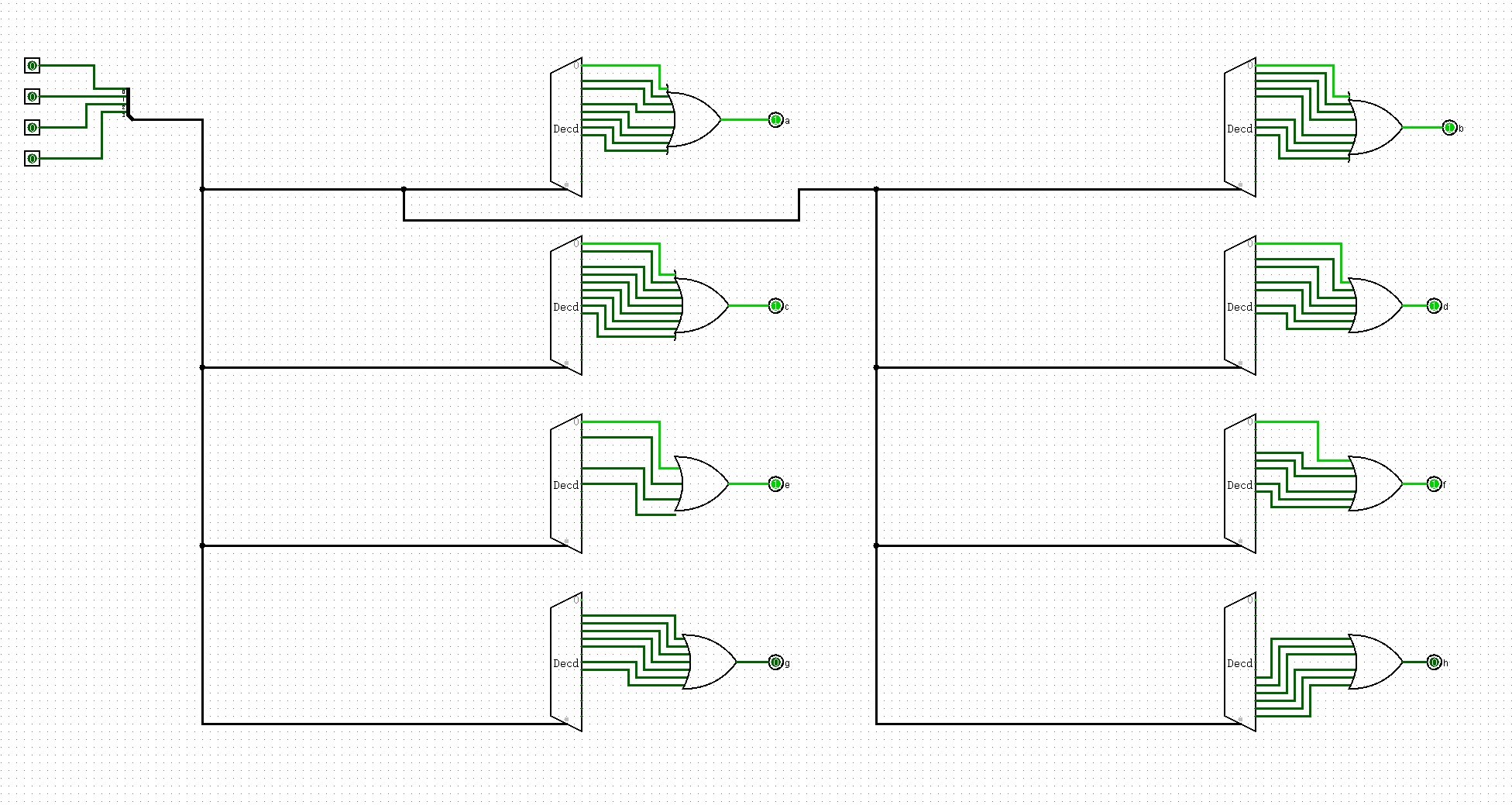

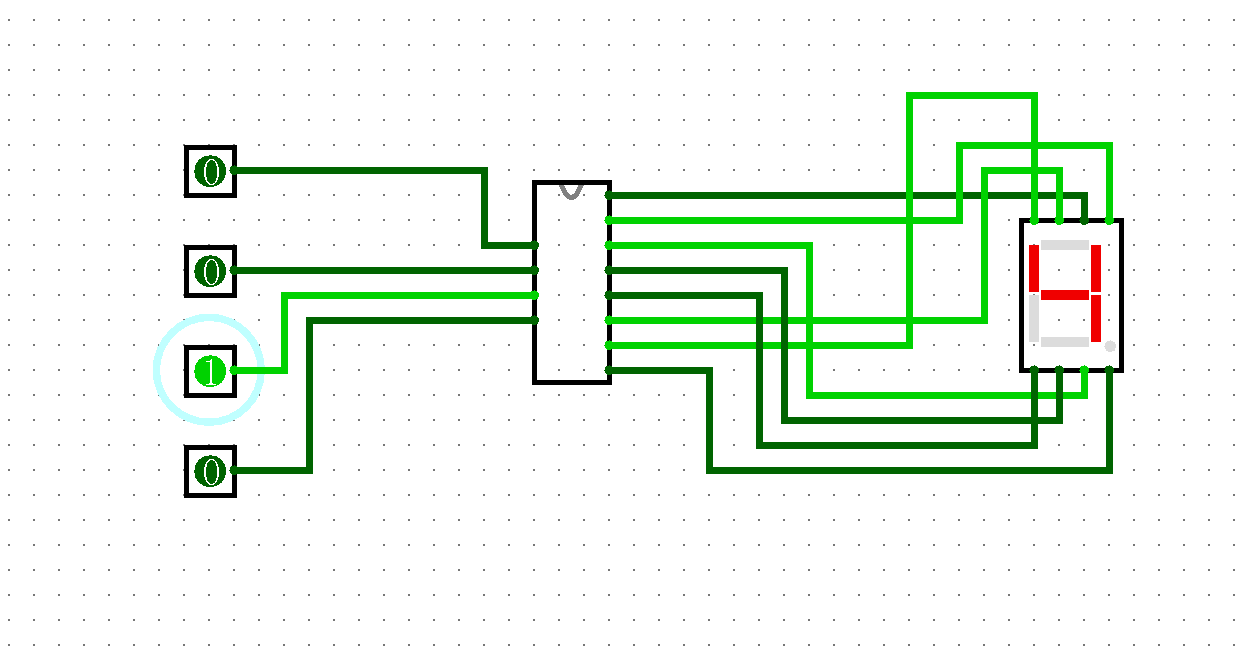

搭建七段数码管译码器

尝试在Logisim中通过门电路搭建一个七段数码管译码器, 它有4位输入和8位输出, 分别与拨码开关和七段数码管相连. 七段数码管译码器支持十进制数字的显示, 即当输入对应0-9时, 七段数码管显示对应的数字; 对于其他输入, 七段数码管只显示小数点. 搭建后, 通过仿真检查你的实现是否正确.

a

---

f| g |b

---

e| |c

--- .h

d

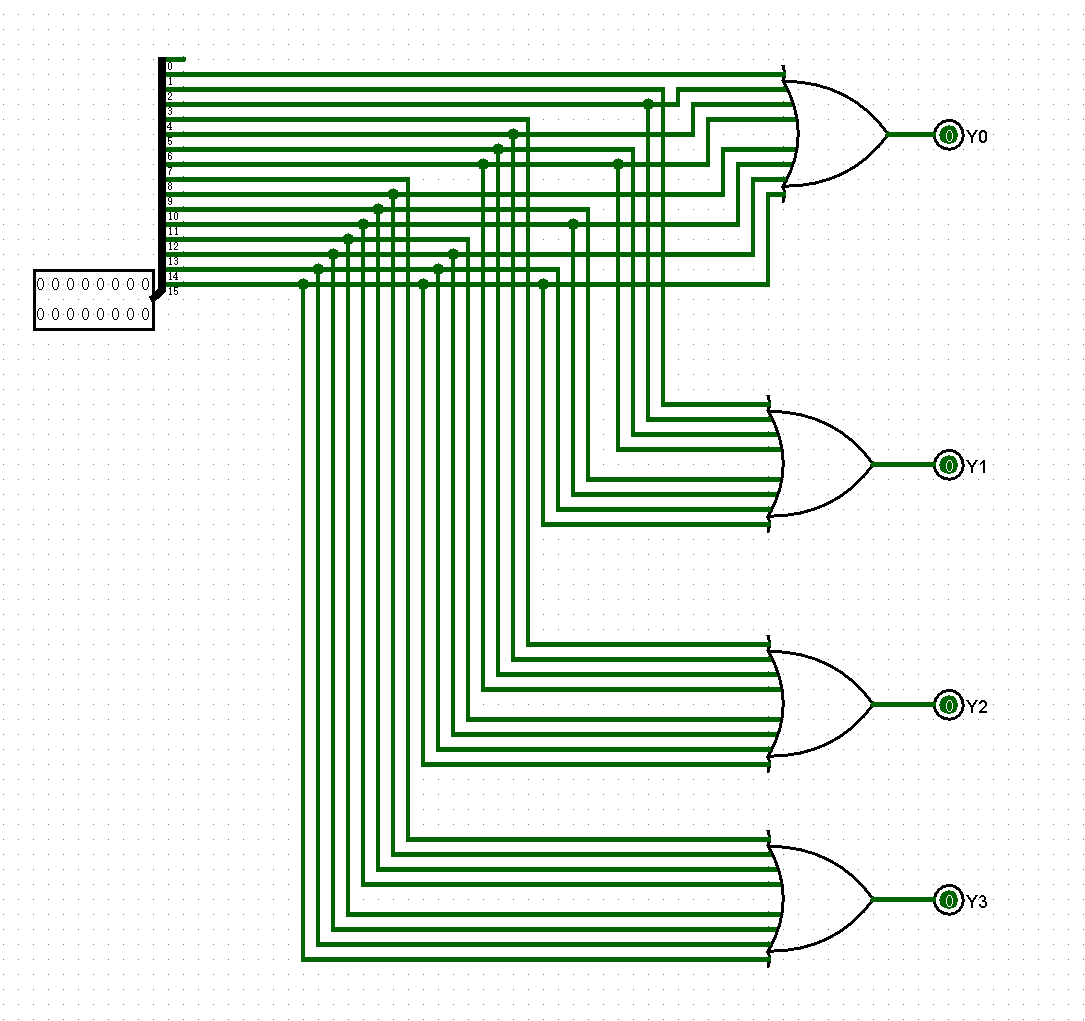

对于4位输入,共有16种状态,我们可以使用8个4-16译码器分别对应8个数码管,然后在4-16数码管后面接上一个n位或门,将某个数码管对应的译码器的“亮”的状态所对应的输出连接到或门上。比如对于a数码管(假设是数码管排列如上图所示),会在0、2、3、5、6、7、8、9共8种状态中点亮,则将4-16译码器对应的输出连接到8位或门,然后将或门的输出连接到a输出端口。七段数码管译码器如下图所示:

将七段数码管译码器连接数码管:

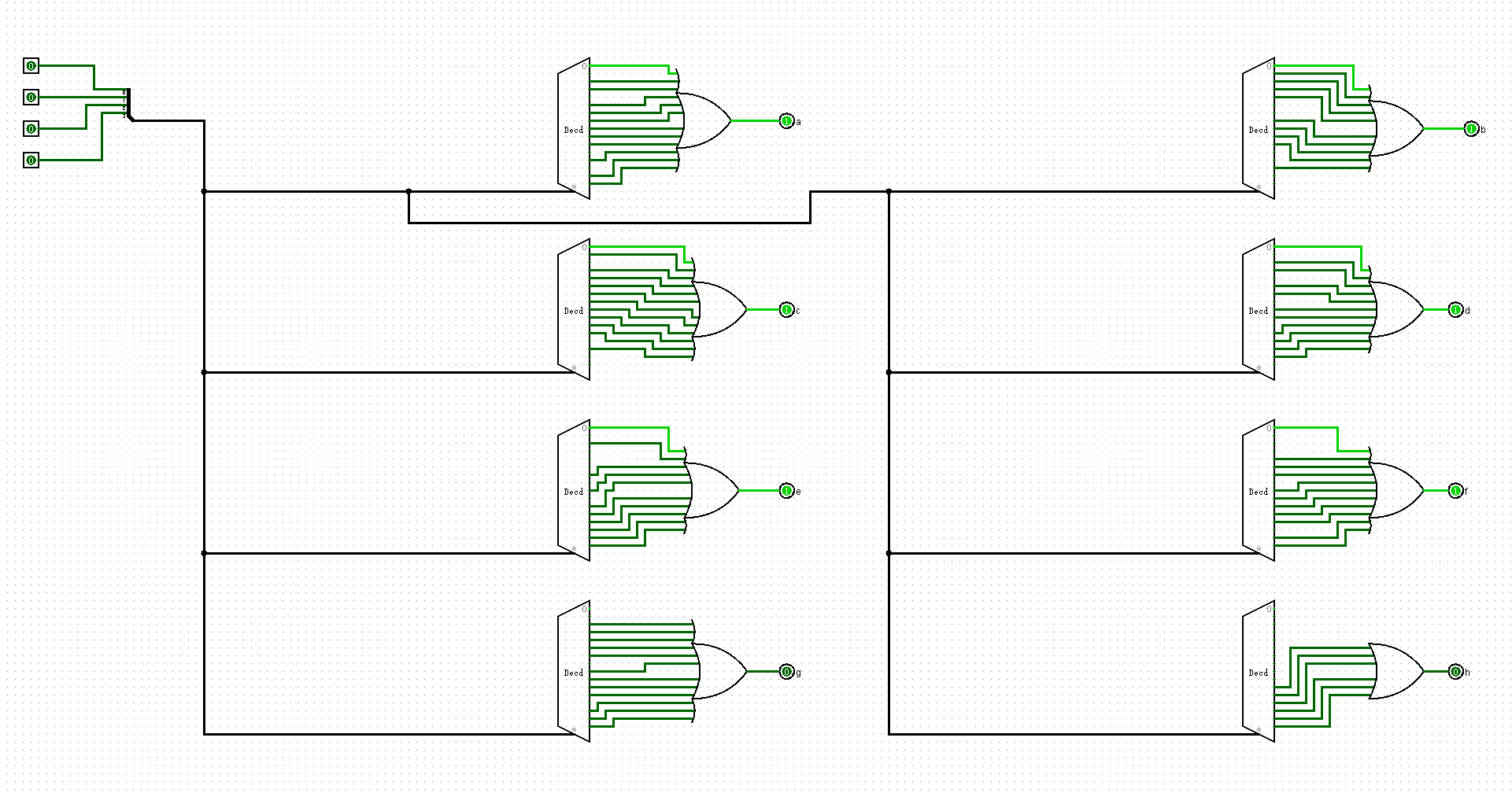

搭建七段数码管译码器(2)

尝试在Logisim中通过门电路搭建一个支持十六进制数字的七段数码管译码器. 和上述的十进制数字相比, 当输入对应10-15时, 七段数码管分别显示A, b, C, d, E, F. 搭建后, 通过仿真检查你的实现是否正确.

这里只需要在上一题的基础上为各个输出添加10-15状态的连线。(这里没有删除小数点的输出)

搭建编码器

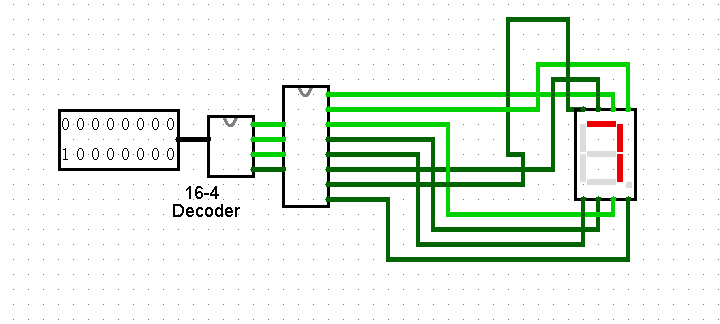

尝试在Logisim中通过门电路搭建一个16-4编码器, 它有16位输入和4位输出, 分别与拨码开关和七段数码管译码器相连, 使得编码器的输出结果通过十六进制数字显示在七段数码管中. 搭建后, 通过仿真检查你的实现是否正确.

16-4编码器门电路如下:

通过七段数码管译码器与七段数码管相连:

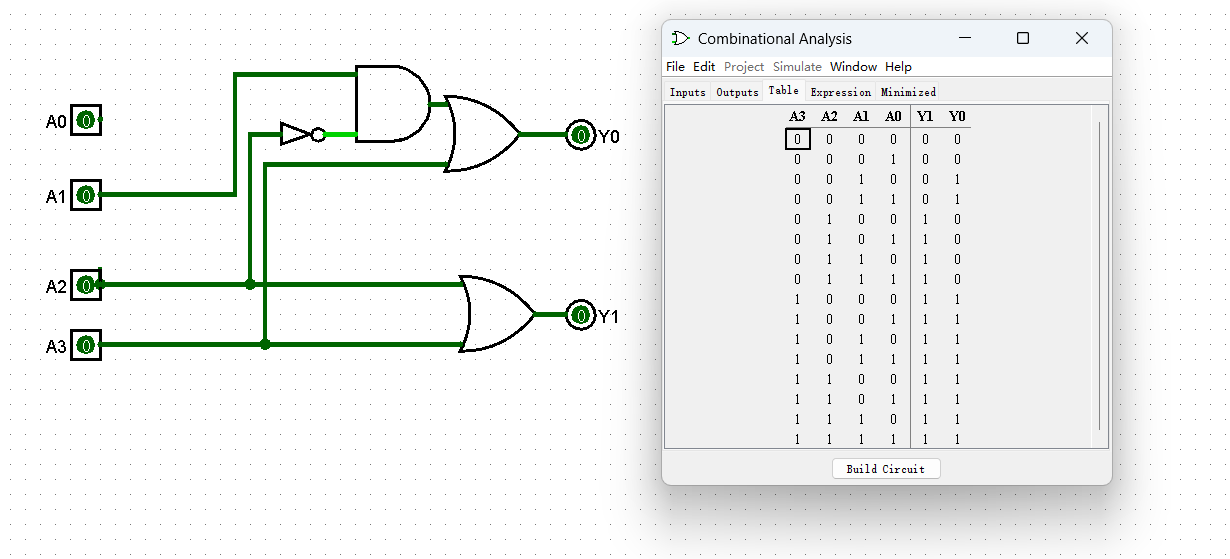

搭建4-2优先编码器

根据上述真值表, 尝试列出每一位输出的逻辑表达式. 然后尝试在Logisim中通过门电路搭建一个4-2优先编码器. 搭建后, 通过仿真检查你的方案是否正确.

实现后, 对比4-2编码器和4-2优先编码器所需的门电路数量.

4-2优先编码器如下图所示,其中使用2个或门、一个与门、一个非门。相对应的4-2编码器进去2个或门。

搭建1位2选1选择器

尝试在Logisim中通过门电路搭建一个1位2选1选择器. 搭建后, 通过仿真检查你的方案是否正确.

搭建3位4选1选择器

尝试画出3位4选1选择器的电路结构图, 然后在Logisim中通过门电路搭建一个3位4选1选择器. 搭建后, 通过仿真检查你的方案是否正确.

所谓3位4选1选择器,就是对四个位数为3的数据进行选择输出的组合电路。在此我们复用之前构造的2-4译码器组件。

3位4选1选择器电路结构如下所示:

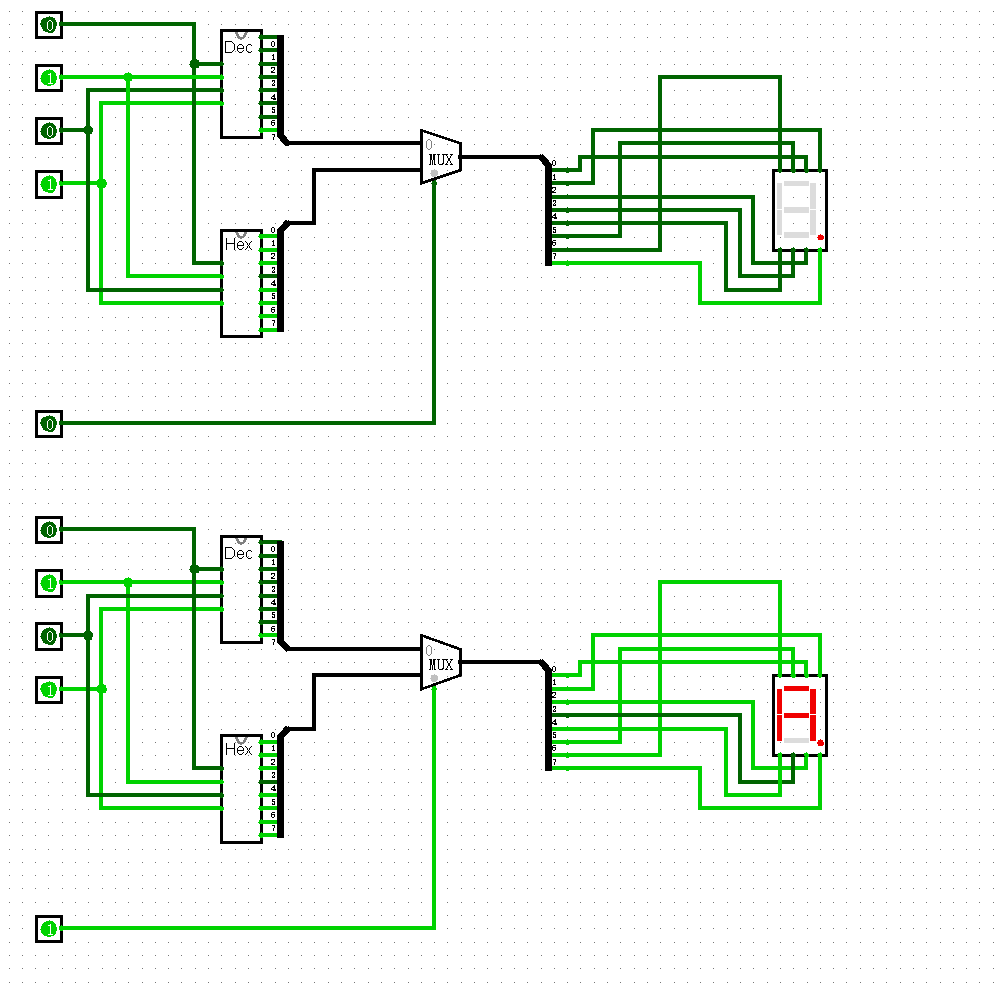

搭建可切换进位计数制的七段数码管

通过5个拨码开关和1个七段数码管, 实现如下功能: 其中4个拨码开关当作数据输入, 剩下1个拨码开关作为进位计数制的选择, 当选择信号为0时, 七段数码管以十进制方式显示数据; 当选择信号为1时, 七段数码管以十六进制方式显示数据. 在输入数据为10-15时, 两种显示方式有所不同.

在此我们复用之前构造的两个七段数码管译码器模块,然后使用一个8位2选1选择器来实现进制切换的功能,这里直接使用Logisim提供的多路选择器来进行构造。

其中显示逻辑与之前的一致,10进制的情况下当输入非0~9时,只点亮小数点。如下图所示:

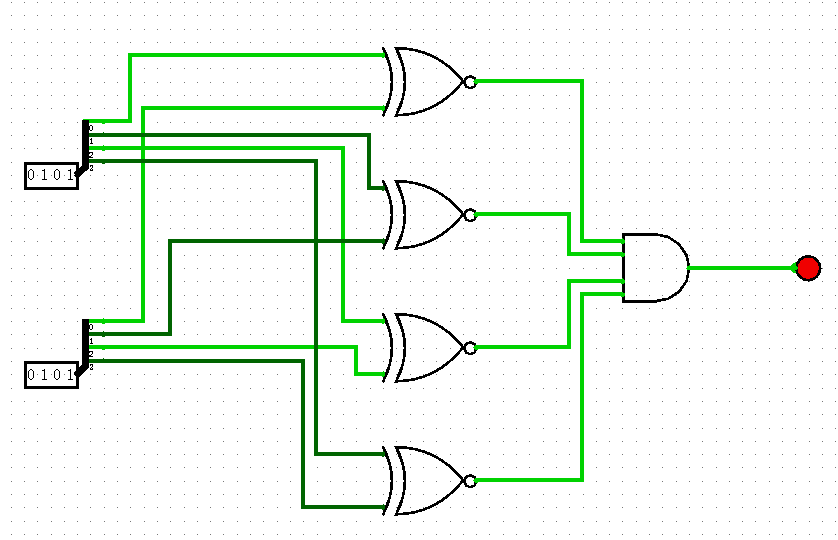

搭建比较器

尝试在Logisim中通过门电路搭建一个4位比较器, 然后通过两组拨码开关对比两组数据是否相等, 若相等, 则点亮一个LED灯. 搭建后, 通过仿真检查你的方案是否正确.

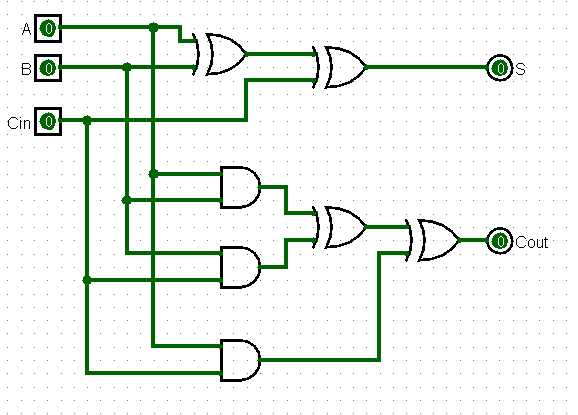

搭建1位全加器

尝试列出1位全加器的真值表, 并在Logisim中通过门电路搭建一个1位全加器. 搭建后, 通过仿真检查你的方案是否正确.

1位全加器真值表如下:

| Cin | A | B | S | Cout |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

电路图如下:

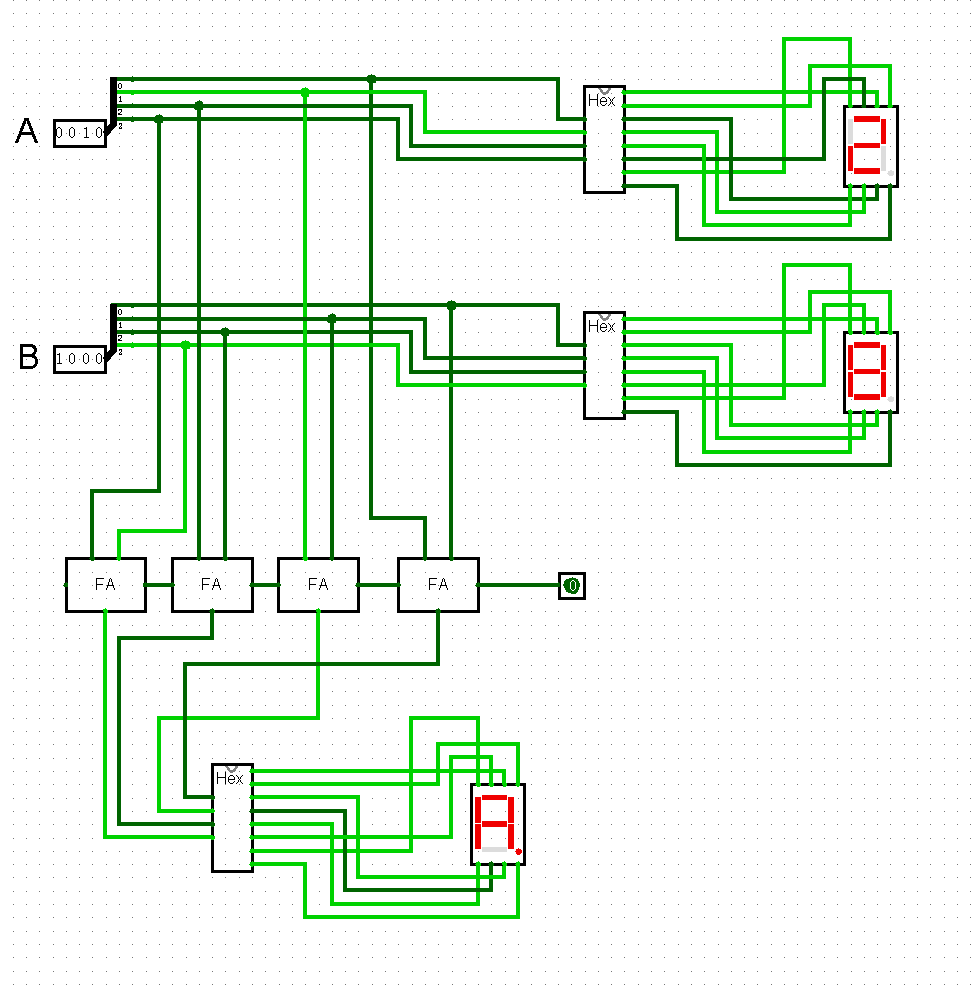

搭建4位加法器

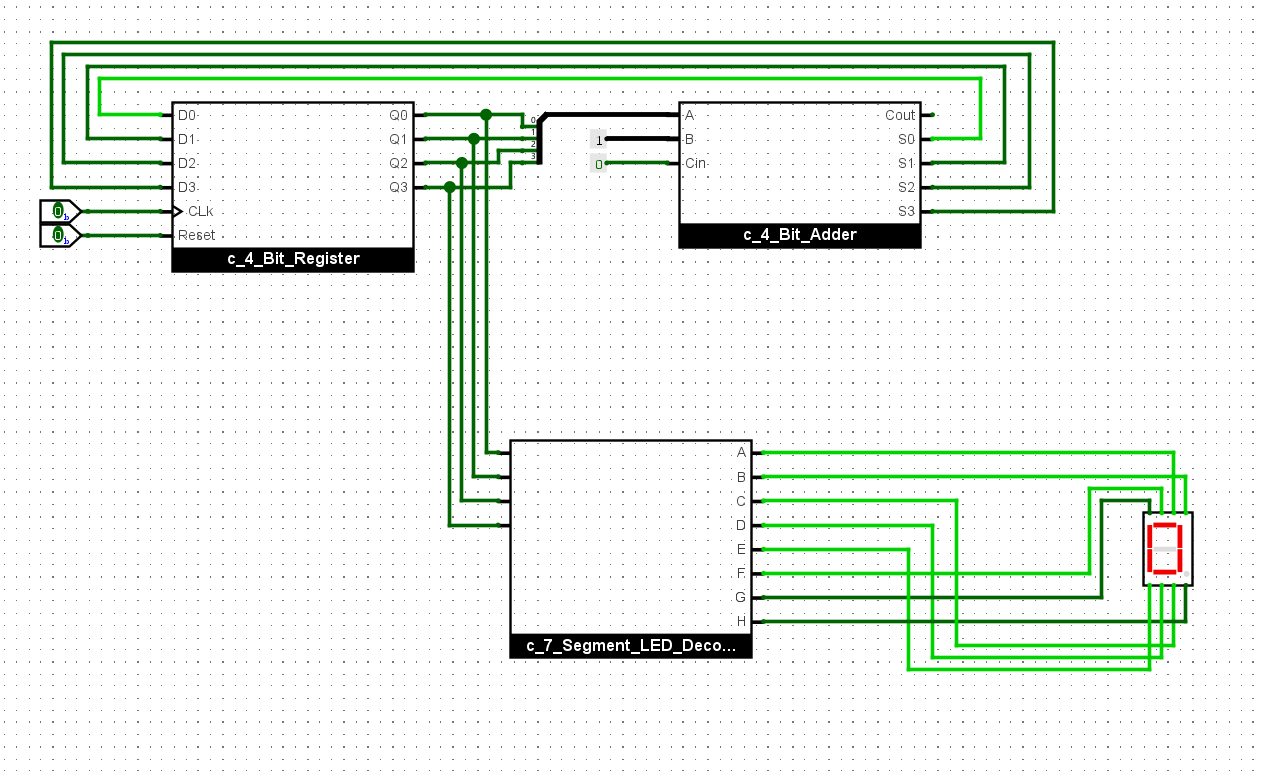

尝试在Logisim中通过门电路搭建一个4位加法器, 用七段数码管按十六进制显示加法器的两个输入和结果, 并用一个LED灯指示加法结果是否产生进位. 搭建后, 通过仿真检查你的方案是否正确.

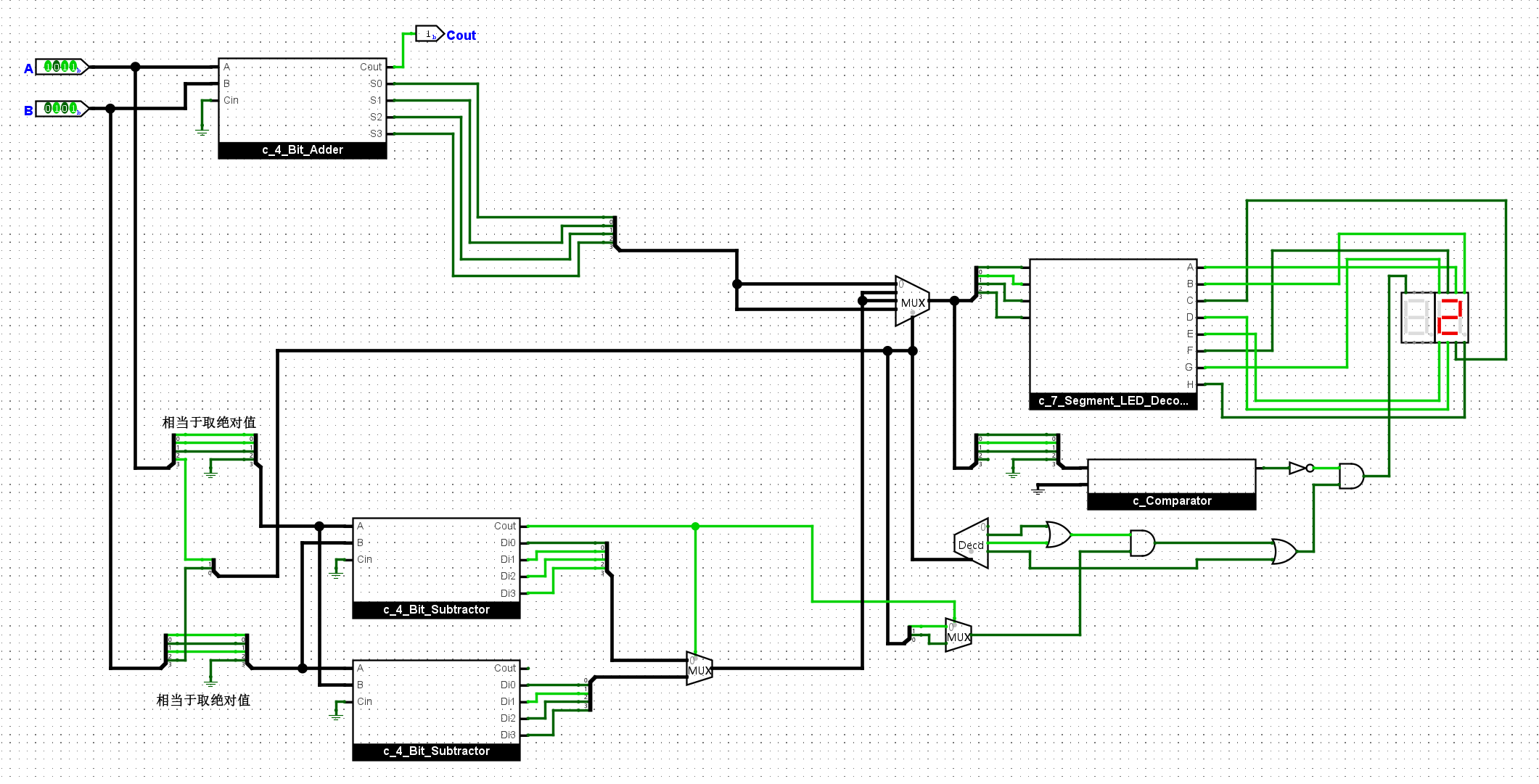

电路如下所示:

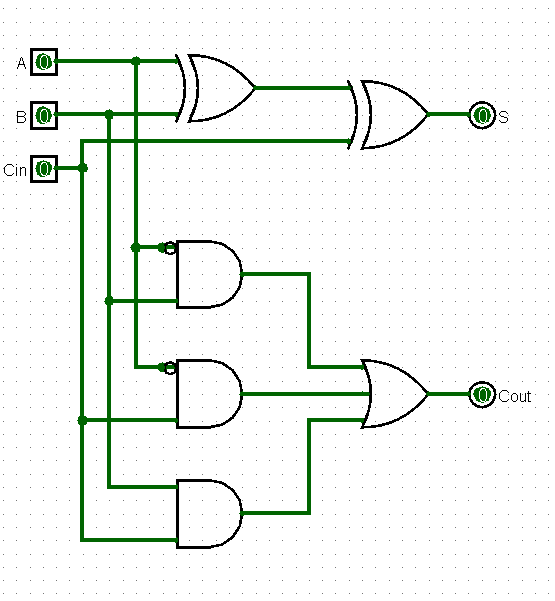

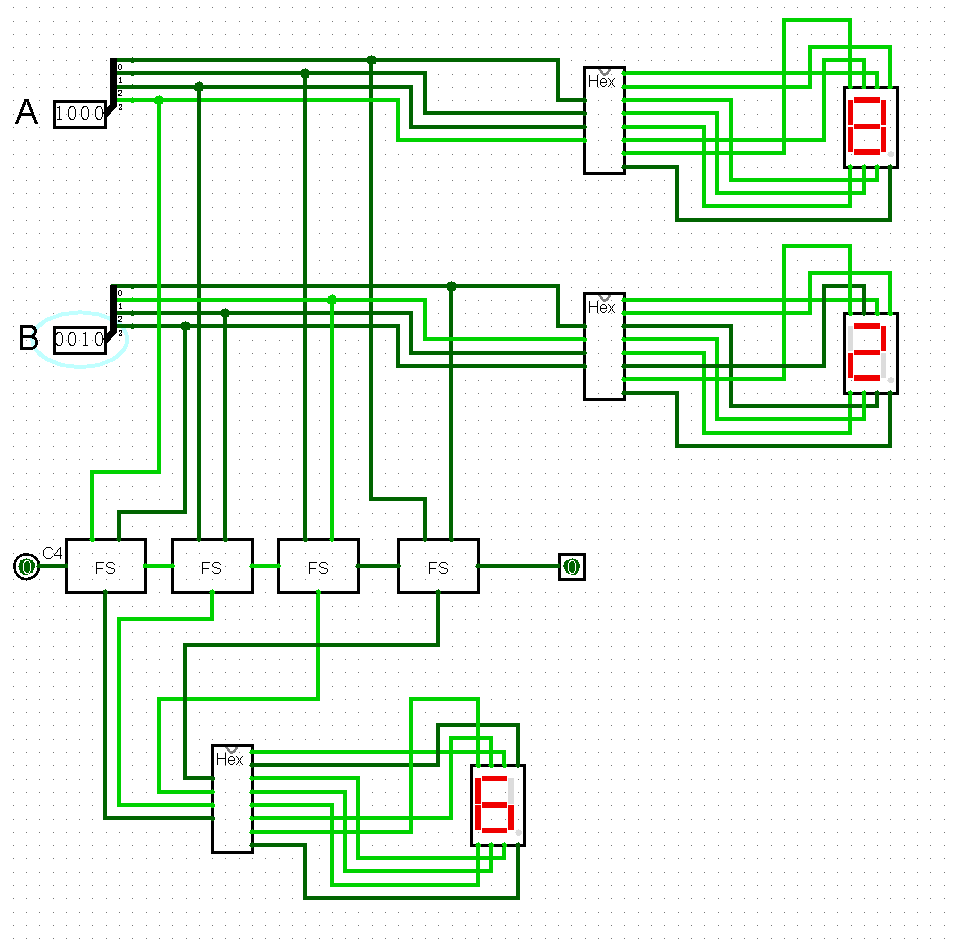

搭建4位减法器

根据4位加法器的设计思路, 尝试在Logisim中通过门电路搭建一个4位减法器, 用七段数码管按十六进制显示减法器的两个输入和结果, 并用一个LED灯指示减法结果是否产生借位. 搭建后, 通过仿真检查你的方案是否正确.

按照加法器的思路,我们首先搭建1位全减器(Full Subtractor),全减器的真值表如下,其中Cin表示来自低位的借位,Cout表示向高位结尾,A为被减数,B为减数:

| A | B | Cin | S | Cout |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

全减器的电路如下:

然后通过1位全减器搭建4位减法器,如下图所示:

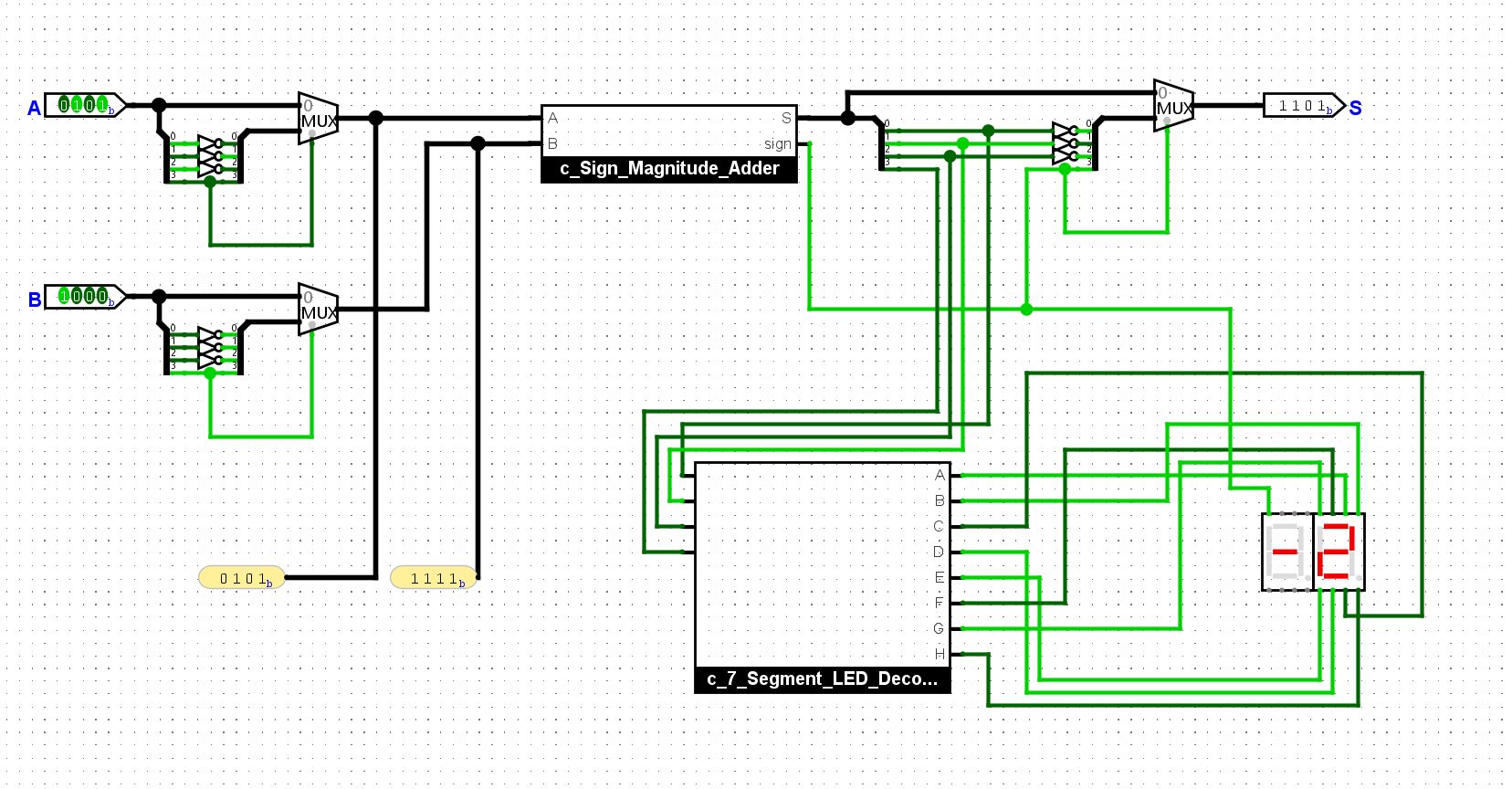

搭建4位原码加法器

理解原码加法器的工作原理后, 尝试用加法器, 减法器和多路选择器等部件, 在Logisim中搭建一个4位原码加法器. 为了显示符号位, 你可以额外实例化一个七段数码管, 结果为负数时显示负号-, 否则不显示. 搭建后, 通过仿真检查你的方案是否正确.

思路如下:

分数字运算和符号选择两个部分考虑。

对于数字运算部分:

- 当两数符号相同时:可以直接将数字输入到4位加法器中。

- 当两数符号不同时:假设

为被操作数, 为操作数,首先对两者取绝对值,得到 和|B|,使用两个减法器 D1和D2,然后将和|B|输入 D1的被减数端和减数端,D2的减数端和被减数端。若D1的借位输出Cout为0,则说明,选择 D1的输出作为运算结果,否则选择D2的输出作为运算结果。

对于符号部分:

- 当两数为正时则使符号位为

0(显像管不显示负号) - 当两数为负时则使符号位为

1(显像管显示负号) - 两数符号不同时,则根据绝对值大小来选择符号,若

D1的Cout输出为0,则说明,选择 的符号位作为输出的符号位,否则选择 的符号位作为输出符号位。 - 此外,当输出的低三位全为

0时,则显像管不显示负号,即显像管不对+0和-0做区分。

电路如下图所示:

搭建4位反码加法器

在Logisim中搭建一个4位反码加法器. 搭建后, 通过仿真检查你的方案是否正确.

在这里我们将反码转为原码,使用之前构造的原码加法器进行运算后再转为反码,电路如下图所示:

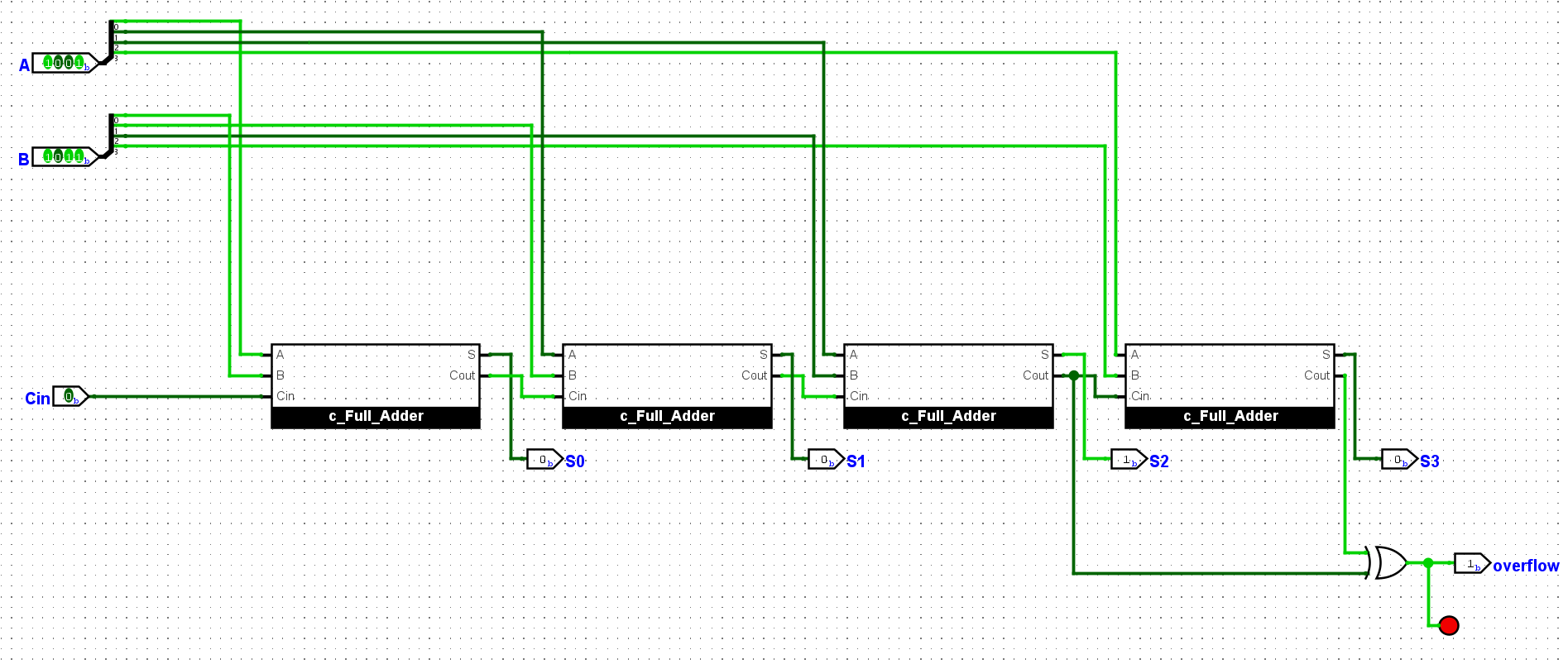

检测补码加法是否发生溢出

| 溢出 | |||||

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 否 |

| 0 | 0 | 1 | 0 | 1 | 是 |

| … | … | … | … | … | … |

将上述真值表补充完整, 尝试列出溢出条件的逻辑表达式. 然后在Logisim中在4位加法器的基础上添加溢出判断逻辑. 添加后, 通过仿真检查你的方案是否正确.

| 溢出 | ||||||

|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 否 | |

| 0 | 0 | 1 | 0 | 1 | 是 | |

| 0 | 1 | 0 | 0 | 1 | 否 | |

| 0 | 1 | 1 | 1 | 0 | 否 | |

| 1 | 0 | 0 | 0 | 1 | 否 | |

| 1 | 0 | 1 | 1 | 0 | 否 | |

| 1 | 1 | 0 | 1 | 0 | 是 | |

| 1 | 1 | 1 | 1 | 0 | 否 |

观察真值表可以发现,只有当运算数符号符号相同,计算结果符号不同时,会发生溢出,而造成这种情况的原因是符号位进位

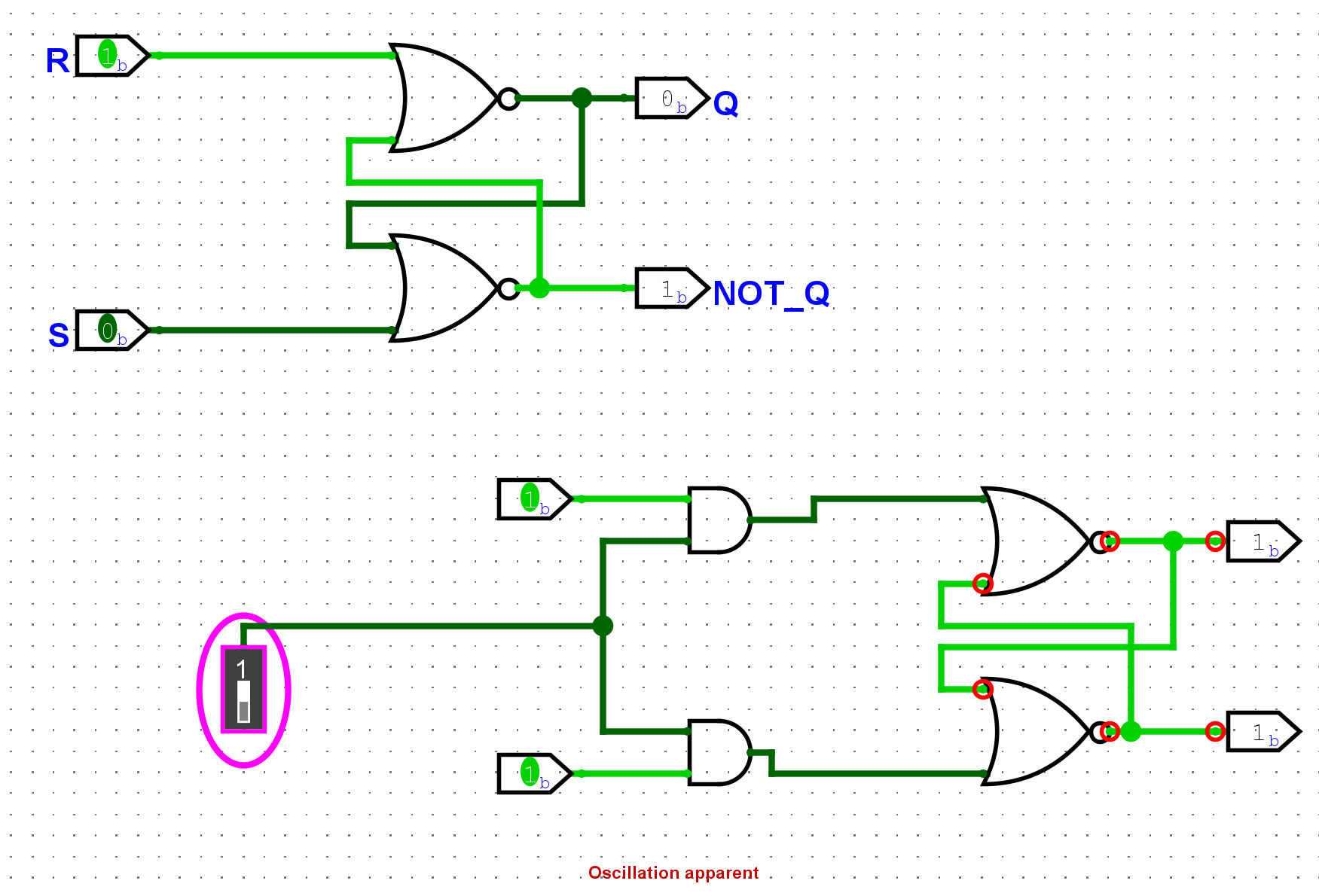

搭建SR锁存器

尝试在Logisim中通过门电路搭建一个SR锁存器. 搭建后, 通过仿真检查你的方案是否正确.

由于手工操作时, 无法通过一次点击直接将两个拨码开关从11变成00. 为了触发亚稳态, 你可以在SR锁存器前额外增加若干与门, 让另一个拨码开关同时控制这些与门的其中一个输入端, 这样就可以通过这一个拨码开关来让SR锁存器的两个输入端同时变成0了. 如果你成功触发了亚稳态, Logisim会在窗口底部显示Oscillation apparent的信息. 此时仿真将无法继续, 你需要通过Logisim的菜单重置仿真.

使用拨码开关和与门使得能让输入从11变为00,实验如图所示:

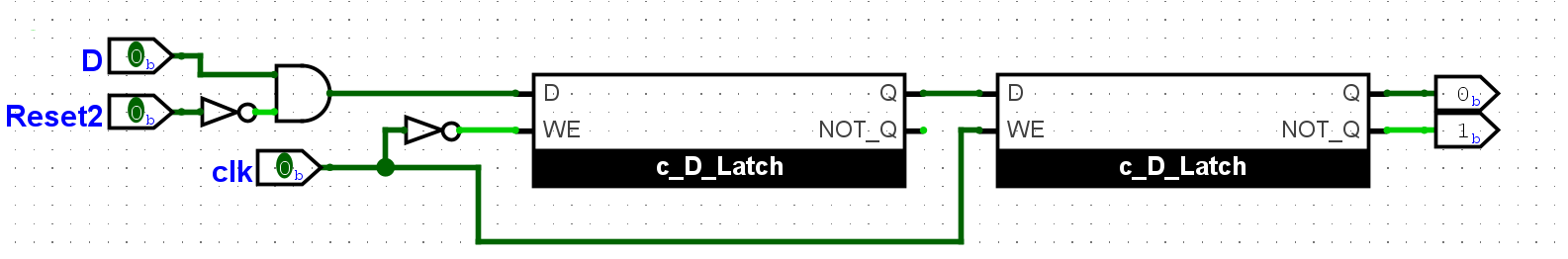

分析D锁存器的行为

尝试根据电路结构图列出真值表,分析D锁存器的行为。

D锁存器的真值表如下:

| 0 | 0 | 0 | 0 | 保持 | |

| 0 | 1 | 0 | 0 | 保持 | |

| 1 | 0 | 0 | 1 | 0 | |

| 1 | 1 | 1 | 0 | 1 |

根据真值表,我们可以得出D锁存器的行为如下:

-

当写使能

WE为0时,D锁存器将保持之前存储的值。 -

当写是能

WE为1时,D锁存器的输出Q将输出D的值。

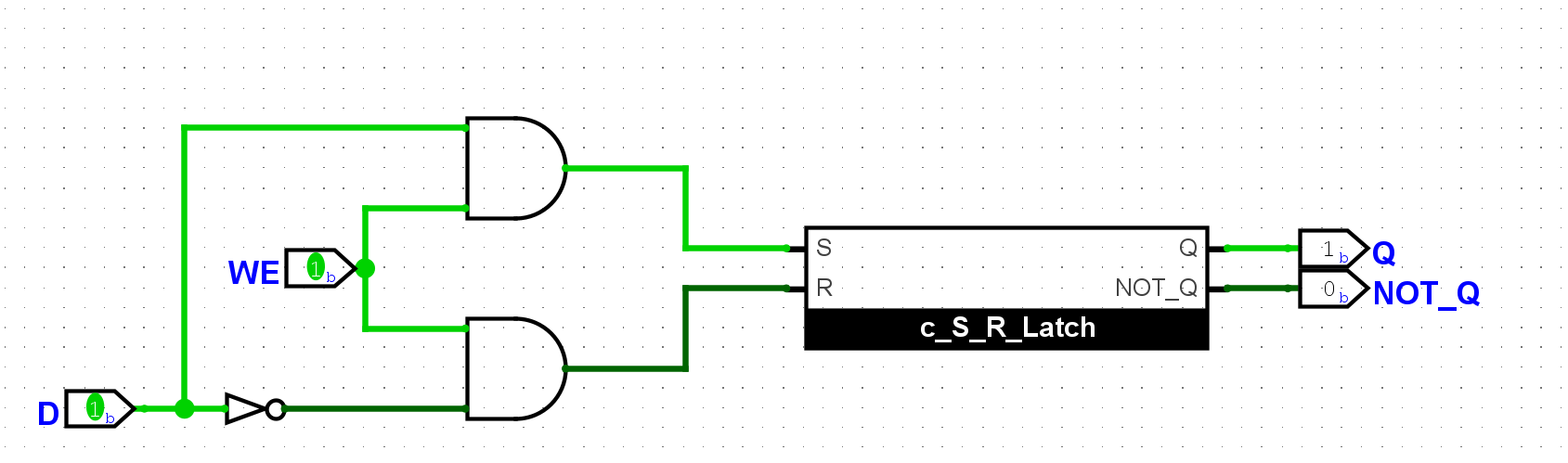

搭建D锁存器

尝试在Logisim中通过门电路搭建一个D锁存器. 搭建后, 通过仿真检查你的方案是否正确.

复用前面搭建的SR锁存器来搭建D锁存器,结构如图:

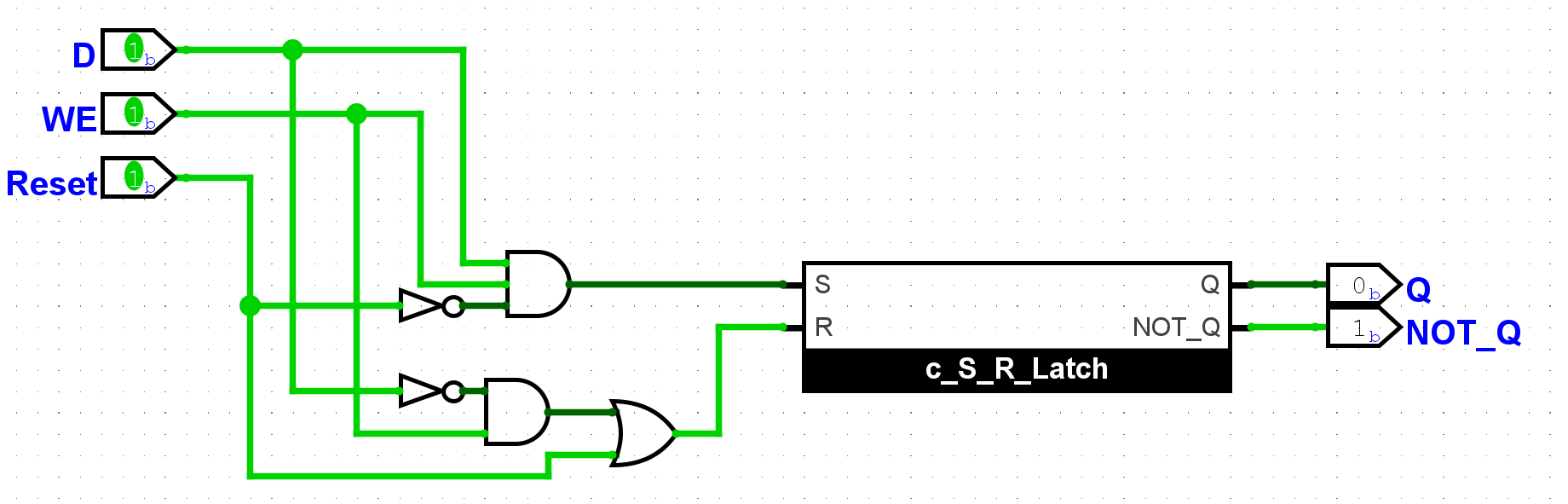

搭建带复位功能的D锁存器

尝试为D锁存器添加一个用于复位的输入端和复位功能. 当复位信号有效时, D锁存器中存放的值将变为0.

复位信号Reset,输入D,使能端WE,以及S、R的真值表如下所示:

| Reset | D | WE | S | R | |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | |

| 0 | 0 | 1 | 0 | 1 | |

| 0 | 1 | 0 | 0 | 0 | |

| 0 | 1 | 1 | 1 | 0 | |

| 1 | x | x | 0 | 1 |

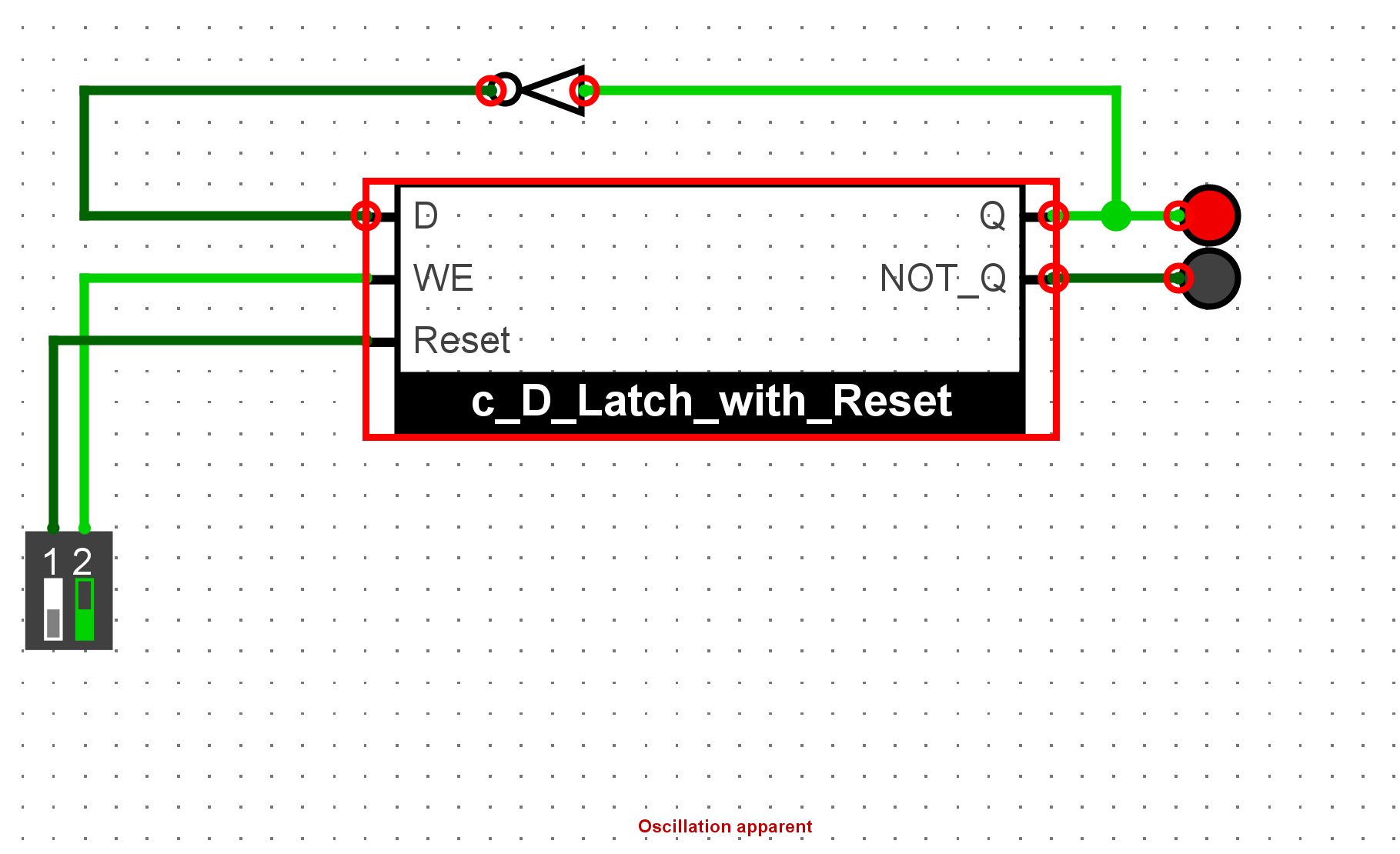

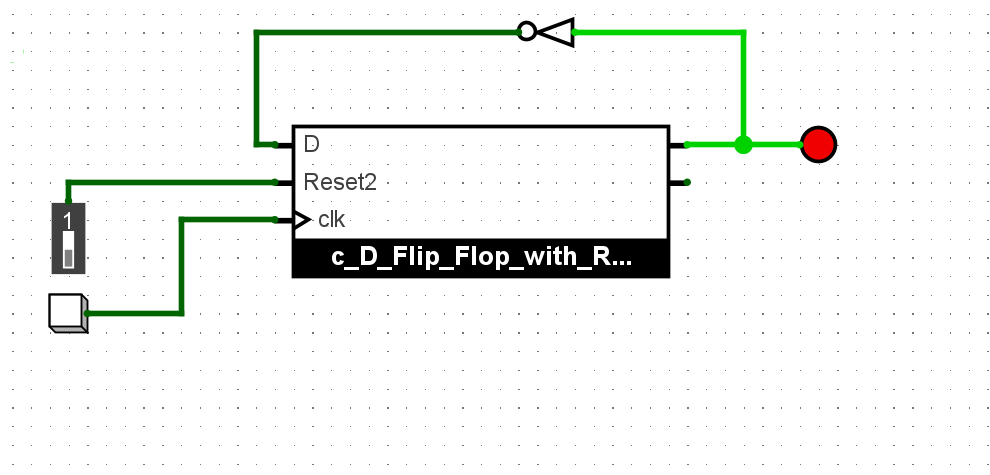

用D锁存器实现位翻转功能

实例化一个带复位功能的D锁存器, 并将其输出取反后作为输入. 我们预期看到D锁存器的输出将在0和1之间反复变化, 但你应该在仿真过程中看到Oscillation apparent的信息, 请分析原因.

如图所示,将复位开关关闭后,出现Oscillation apparent。

因为在使能期间,输入D随时能传到Q,因此当D变反后,Q也会立刻变反,导致D和Q在使能期间高速切换状态,仿真器无法反应这种高速变化,因此出现Oscillation apparent。

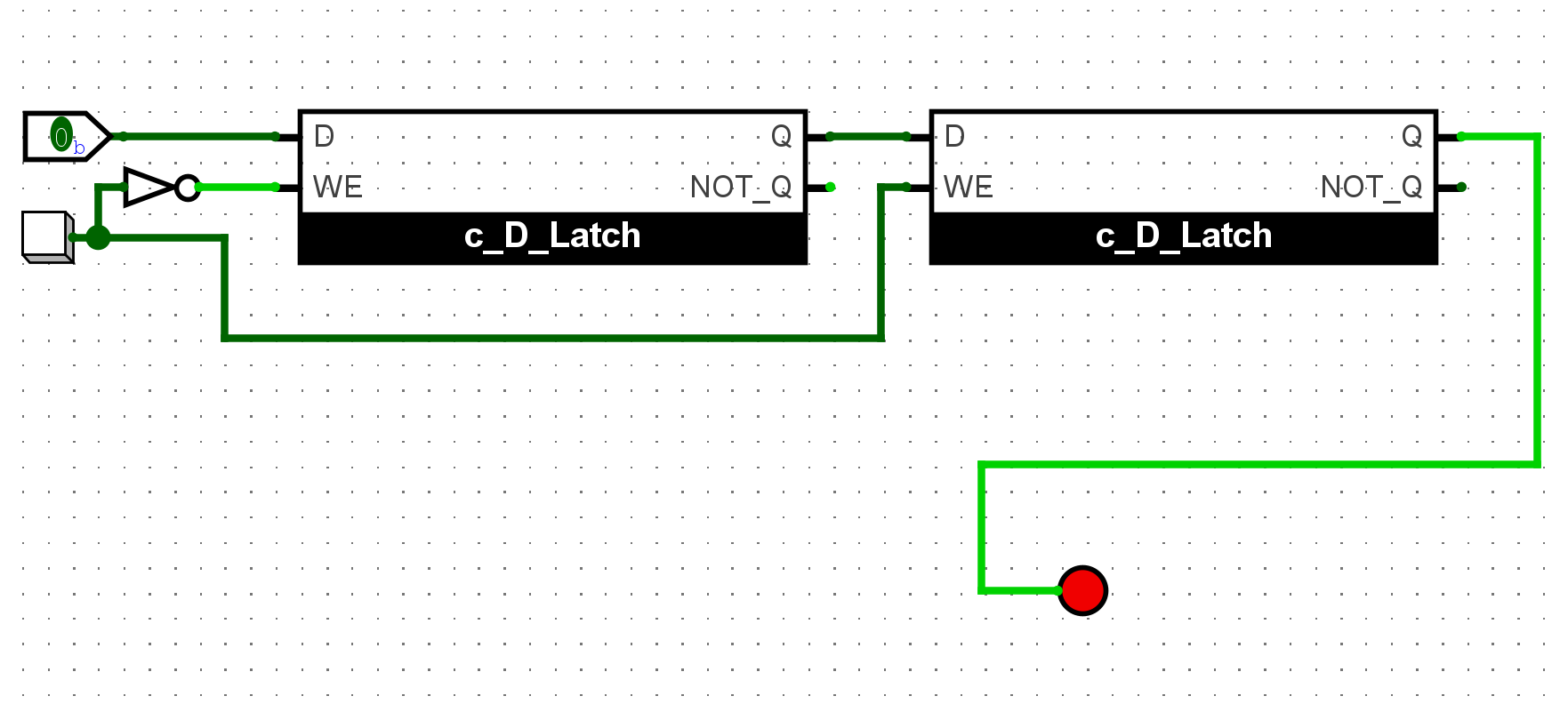

搭建D触发器

尝试在Logisim中通过门电路搭建一个D触发器. 搭建后, 将时钟端口与一个按钮相连, 按钮的按下和释放分别会产生高低电平, 因此点击一次按钮可产生一个脉冲, 以此来充当时钟信号. 尝试长按按钮, 来观察主从式D触发器的工作过程.

电路如图所示,观察可以发现当按钮按下的瞬间主锁存器的输出被输入到从锁存器。

搭建带复位功能的D触发器

尝试为D触发器添加一个用于复位的输入端和复位功能. 当复位信号有效时, D触发器中存放的值将变为0.

通过改变主锁存器的输入来实现,需要等时钟信号下一个上升沿来临时才能复位。

电路如下图所示:

用D触发器实现位翻转功能

实例化一个带复位功能的D触发器, 并将其输出取反后作为输入. 我们预期看到D触发器的输出将在0和1之间反复变化. 尝试和上文D锁存器的结果进行对比.

这一次可以顺利进行位翻转,因为D触发器的输出变化频率受到clk输入限制,Logisim可以正常模拟。

电路如下图所示:

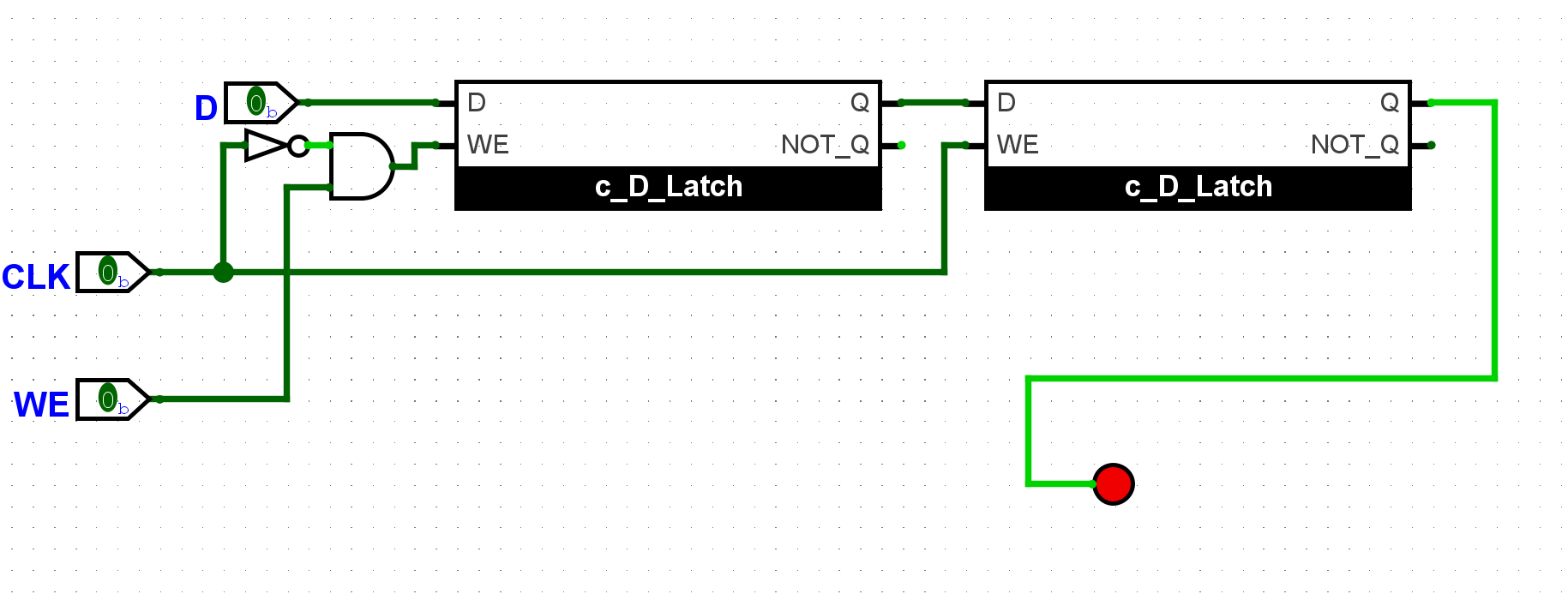

搭建带使能端的D触发器

尝试在Logisim中通过D触发器和若干电路, 搭建一个带使能端的D触发器. 搭建后, 通过仿真检查你的方案是否正确.

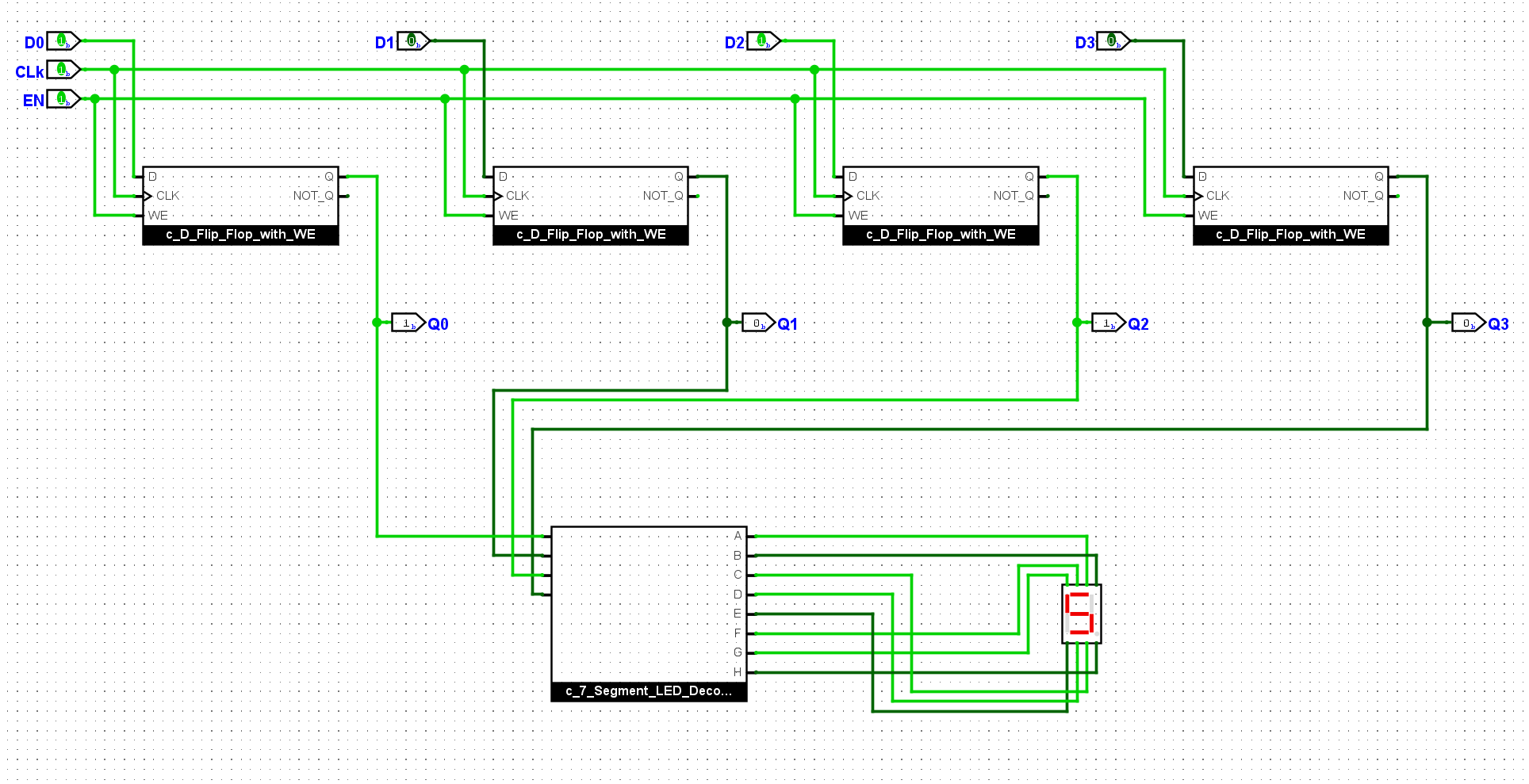

搭建4位寄存器

尝试在Logisim中通过D触发器搭建一个4位的寄存器, 具备复位功能. 搭建后, 尝试从拨码开关向寄存器写入4位数据, 并将寄存器的输出接到七段数码管进行显示.

电路如下图所示:

搭建4位计数器

通过上述4位寄存器和之前搭建的加法器, 实现一个4位计数器, 每次时钟到来时, 寄存器中的值加1, 加到最大值时重新从0开始. 在Logisim中, 你可以通过元件库中的Wiring(线路)类别下的Constant(常数)元件实例化一个常数, 具体使用方式请RTFM.

电路如下图所示:

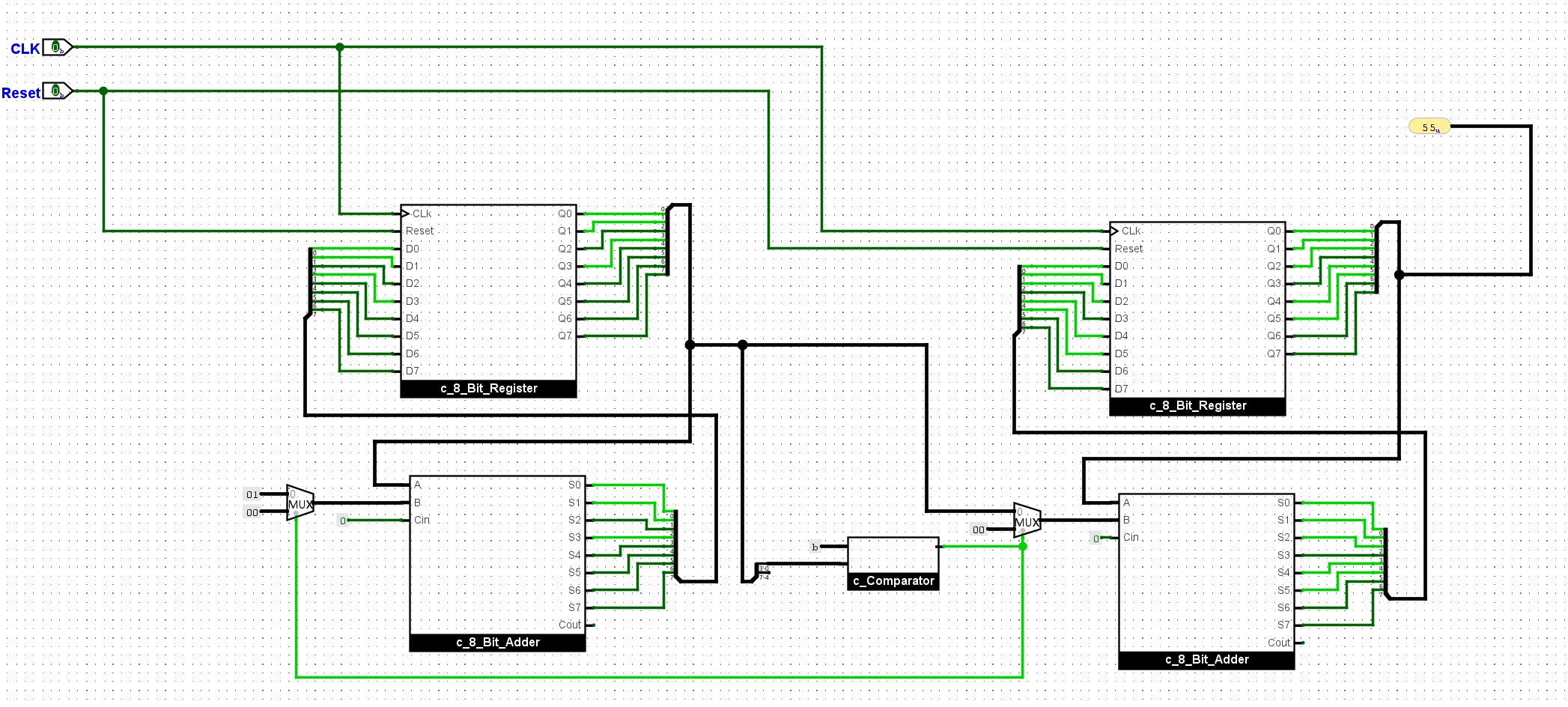

搭建求和电路

尝试通过寄存器和加法器, 计算出1+2+...+10的结果. 为了容纳计算结果, 你可以考虑实现8位的寄存器和加法器.

电路图如下所示:

实现电子时钟

利用寄存器和七段数码管, 实现一个电子时钟, 具备"分"和"秒"的功能.

具备"分"和"秒"的功能的功能共需要4个数,其中(从右向左数)第1位和第3位逢10向后一位进1并将自身清零,第2位逢6向后一位进1并将自身清零,第4位逢6清零。

我们可以使用之前构造的4位寄存器来存储数字。使用Logisim提供Clock作为时钟,其中将High Duration和Low Duration都设置为1 Tick,并在Simulation中将Auto-Tick Frequency设置为2Hz。

然后使用4位比较器进行数值比较来判断是否进位和清零,比如逢6进1,因为需要在下一个时刻进位,所以我们应该让寄存器的数值与5比较,让下一个上跳沿来临时比较器的输出是1,另外除了第一位是直接通过是否相等来进行判断,其他位应该还需要再判断是否有进位,即既要满足比较器相等也要满足有进位产生。

电路图如下所示: