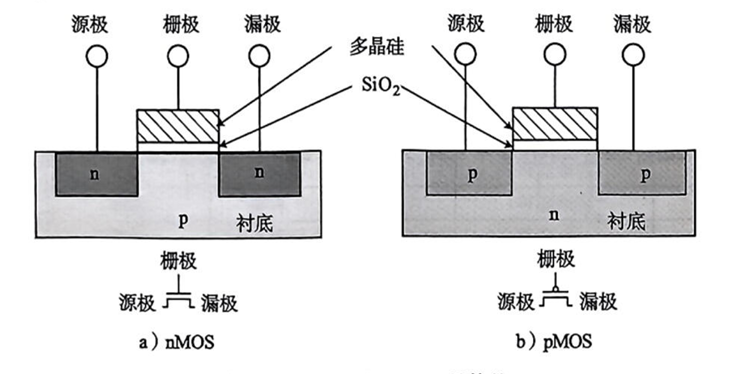

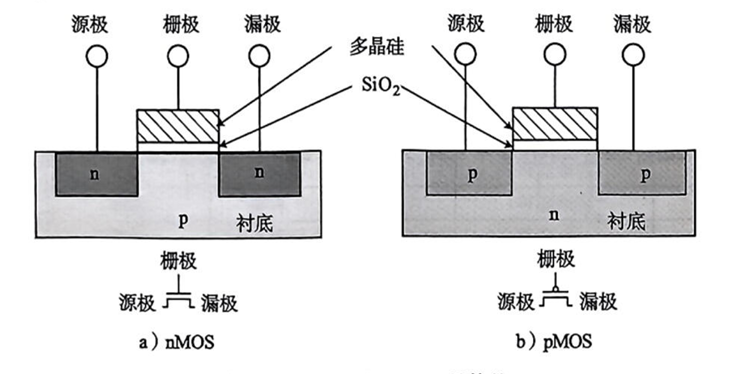

MOS 晶体管

MOS 晶体管包括底层叫作半导体衬底(substrate)的硅晶圆片、上层的导电栅(gate)和中间二氧化硅构成的绝缘层。

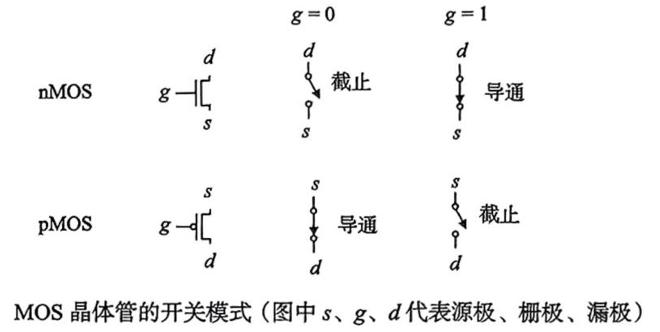

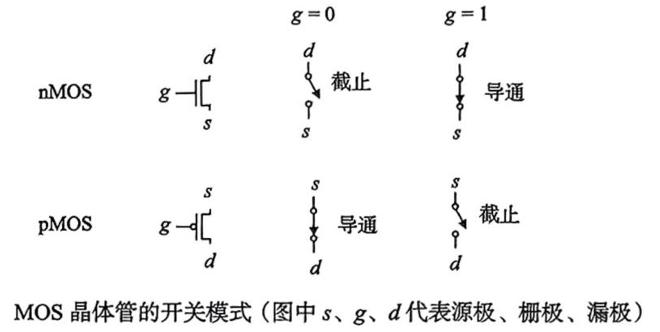

MOS 晶体管有两种类型,即 nMOS 和 pMOS。当 pMOS 晶体管的衬底电压为 时,若栅极电压为 ,则晶体管处于截止状态;若栅极接地,则晶体管处于导通状态。nMOS 管与 pMOS 管的工作原理相反。

但是 MOS 晶体管并不是完美的开关,nMOS 晶体管虽然能够很好地导通低电平,但其导通高电平的能力比较弱,同样,pMOS 晶体管导通高电平的能力虽然很好,但其导通低电平的能力较弱。

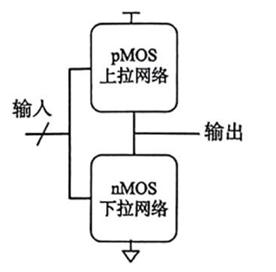

CMOS 组合电路设计方法

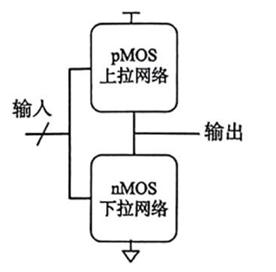

CMOS组合电路可以分上拉网络(PUN)和下拉网络(PDN)两部分来构造。nMOS 晶体管可以很好地导通低电平,因此由 nMOS 构成的下拉网络连接输出和 GND, 从而将输出下拉到低电平。pMOS 晶体管可以很好地导通高电平,因此由 pMOS 构成的上拉网络连接输出和 ,从而将输出上拉到高电平。网络由串联或并联的晶体管构成,只要任一并联的晶体管导通,网络就导通;只有所有串联的晶体管导通,网络才能导通。

如果上拉网络和下拉网络同时导通, 和 GND 之间将会产生短路(shortcircuit)。门输出电压可能处于禁止区域,损耗大量功率的晶体管很可能被烧毁。反过来,如果上拉网络和下拉网络同时截止,门输出既不能连接到 ,也能不连接到 GND , 此时输出是浮空的(float)。

因此我们可以这样设计逻辑电路:假设逻辑表达式为,且逻辑表达式为反逻辑(反逻辑的意思是逻辑表达式最外层带有 ,如果是正逻辑,则在则先添加 使其变为反逻辑,按照反逻辑构造出电路后再在电路的输出增加反相器)。先使用 nMOS 画出 PDN :nMOS 网络表达的是 输出为 0 时的逻辑,当 输出为 0 时,我们希望 PDN 导通,当 为 1 时,我们希望 PDN 关断(此时 PUN 导通)我们可以先对取反,获得 ,然后根据 G,按照串与并或(如果输入带非号,先接反相器再接 nMOS,如 , 应该先接反相器)的方法画出电路图。

因为 nMOS 晶体管一般连接 GND 和输出构成下拉网络,因此,假设 表示 PDN 导通,则 时输出为 ,即 与 是相反的,因此我们对 取反获得 可以更直观地描述电路,此时变为 时输出为。nMOS 输入为 1 时导通,输入为 0 是关断,此时 PDN 上的各个 nMOS 对于电路来说可以视作开关,1 表示开关闭合,0 表示开关关闭,逻辑与关系可以表示为开关串联,逻辑或可以表示为开关并联。

再根据 PDN,互补画出 PUN(不取反,串与并或,如果输入不带非号,先接反相器再接 nMOS)。

以上方法由博主按照自己的理解归纳出来,且按此方法得到的电路不一定是最优的,仅供参考,若有错误还请指出。

以 为例,我们首对 取反获得 ,然后根据 搭建 nMOS 网络,首先将输入 连接到一个反相器,获得 ,再将 和 并联。然后根据 构建 pMOS 网络。

%E7%94%B5%E8%B7%AF.png)

参考

1.Digital Design And Computer Architecture

2.胡伟武 计算机体系结构(第二版)

%E7%94%B5%E8%B7%AF.png)